一、ARM体系结构

程序编译的过程:

预处理(.c-.i):宏替换,头文件展开,去掉注释,特殊符号的处理

编译(.i-.s):C语言转换成汇编语言

汇编(.s-.o):汇编转成成二进制文件

链接(.o-app):关联各种符号信息,归并文件,将不可执行二进制文件转换成可执行二进制文件

1、最小系统:电源、时钟(晶振)、复位、内存、Flash、输入输出

ROM:只读存储,访问速率慢,掉电数据不丢失

RAM:随机存储,访问速率快,掉电数据丢失

flash:结合RAM和ROM的优点的存储

SRAM:静态随机存储

DRAM:动态随机存储

SSRAM:同步静态随机存储

SDRAM:同步动态随机存取存储器

DDRn:双倍速率同步动态随机存取存储器

PROM:可编程ROM

EPROM:可擦除PROM

EEPROM:电可擦除PROM

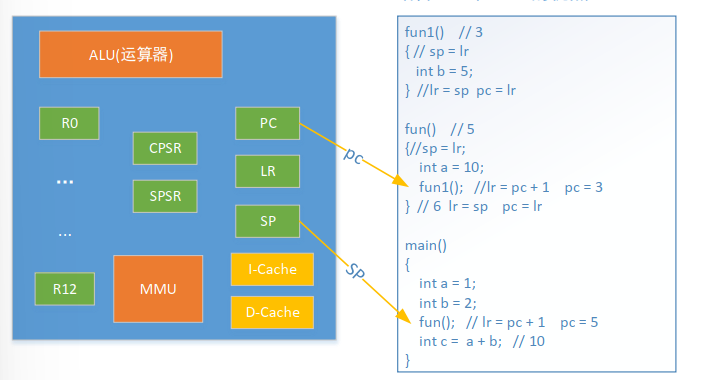

2、CPU:中央处理单元

CU:处理单元//

ALU:运算单元,实现基本的运算单元

R0-R12:通用寄存器,存储数据

PC:程序计数器,指向正在执行的下下条指令,上电默认做自加运算

LR:链接寄存器,保存函数的返回地址

SP:栈指针寄存器,指向栈顶

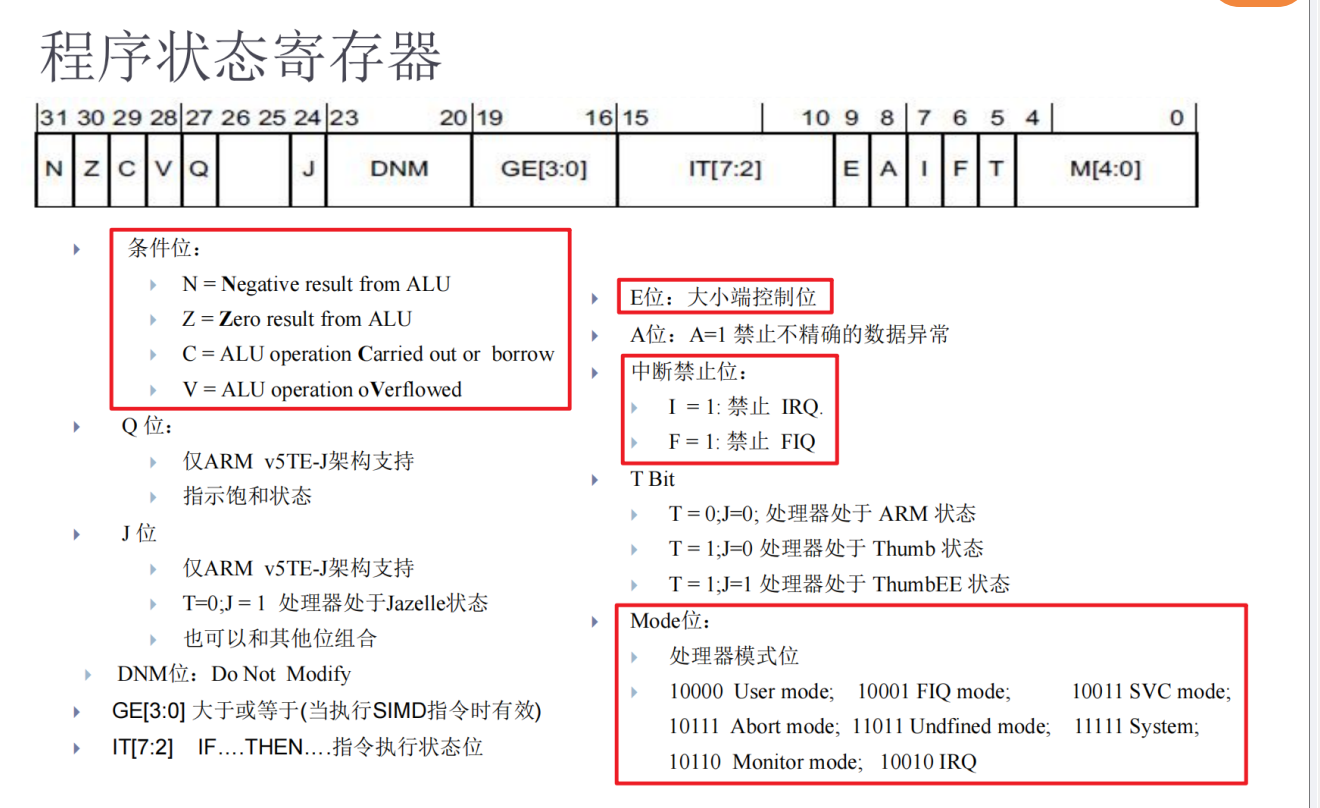

CPSR:当前程序状态寄存器,运算的结果为0、正、负等,运算中产生的进位、借位等;中断使能,工作状态、工作模式。

SPSR:保存程序状态寄存器,存放CPSR的备份

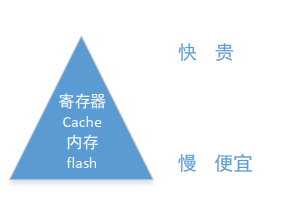

Cache: CPU和内存之间的缓存,访问速率远高于内存

MMU: 内存管理单元,做虚拟地址到物理地址的转换

3、处理器

有几个CPU就有几核

多核异构:同一个处理集成不同架构的CPU

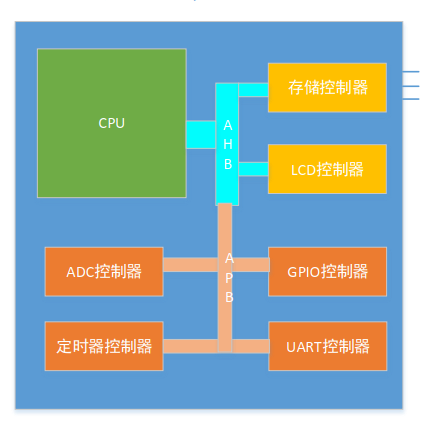

SOC:片上系统(下图)

AHB:高速总线

APB:外设总线(低速)

RISC:精简指令集(使用20%的指令实现80%的功能)

CISC:复杂指令集(使用100%的指令实现100%的功能)

cortex-A:低功耗、消费类电子

cortex-R:实时性、军工、汽车

cortex-M:高性能、偏控制

DSP:数字信号处理器

FPGA:现场可编程门阵列

4、三大总线(外设)

地址总线:传输地址(单向)

数据总线:传输数据(双向)

控制总线:读写、忙

5、三级存储系统

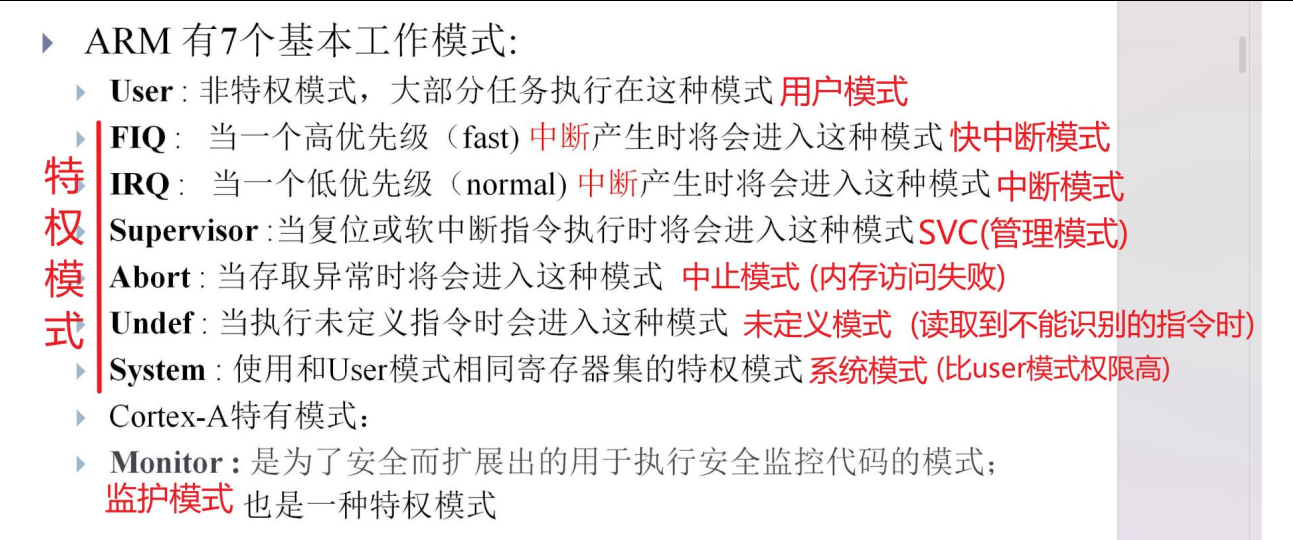

6、处理器工作模式

特权模式权限比非特权模式高

FIQ>IRQ

7、程序状态寄存器CPRS SPRS

N:结果是否-,Z:结果是零0

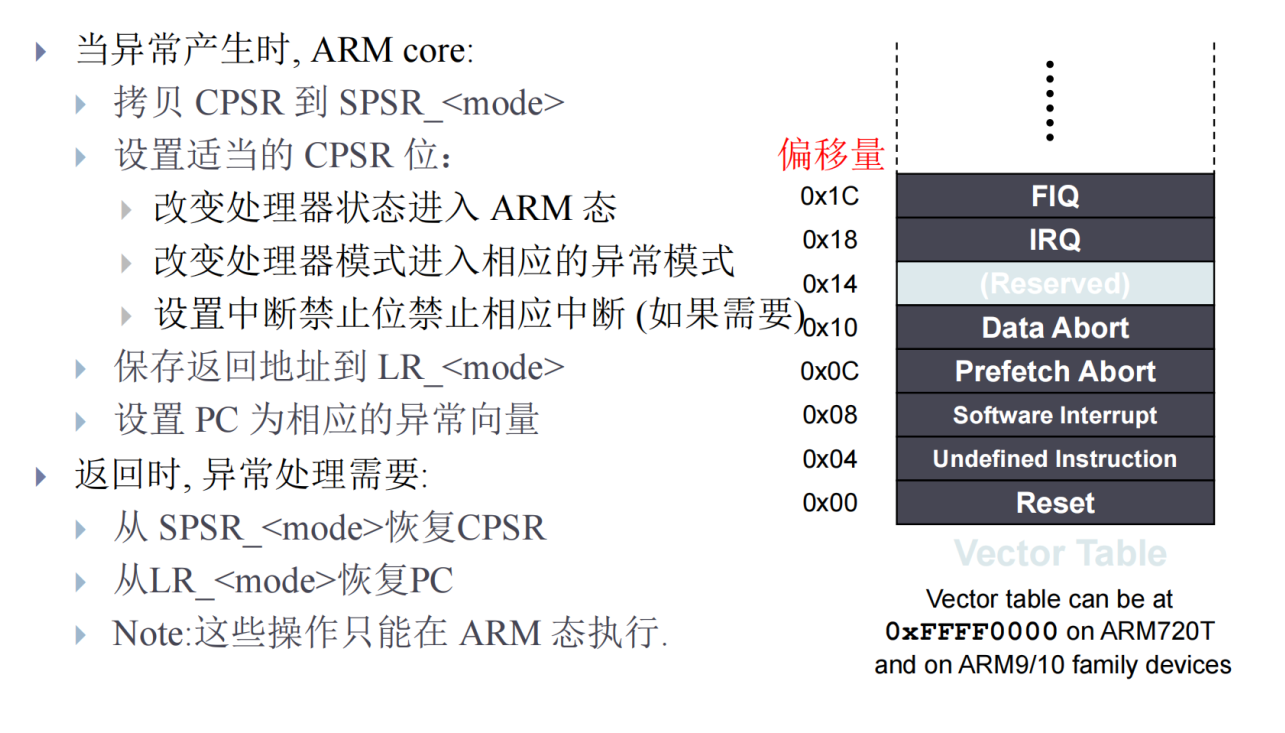

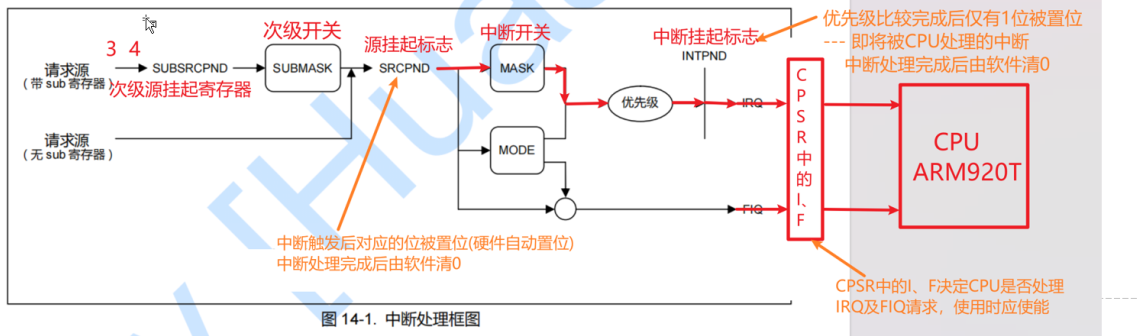

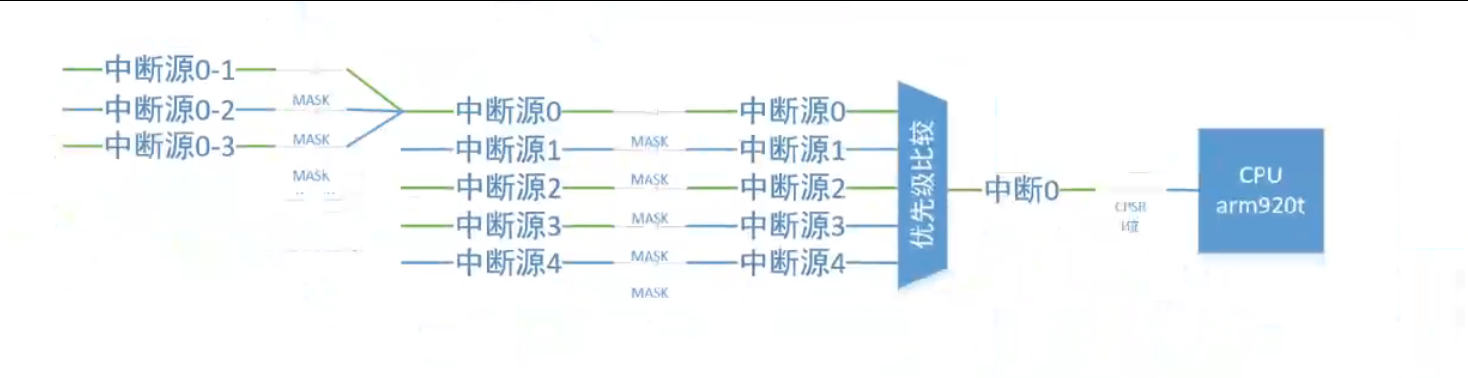

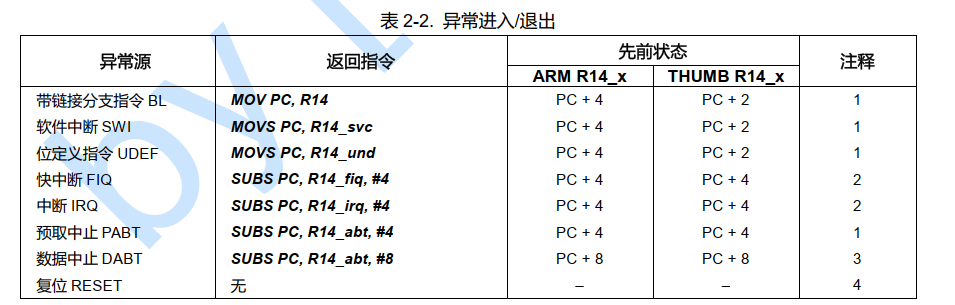

8、异常处理

三级流水线:预处理、解码、执行

ARM汇编语言

二、汇编

1、ARM指令集

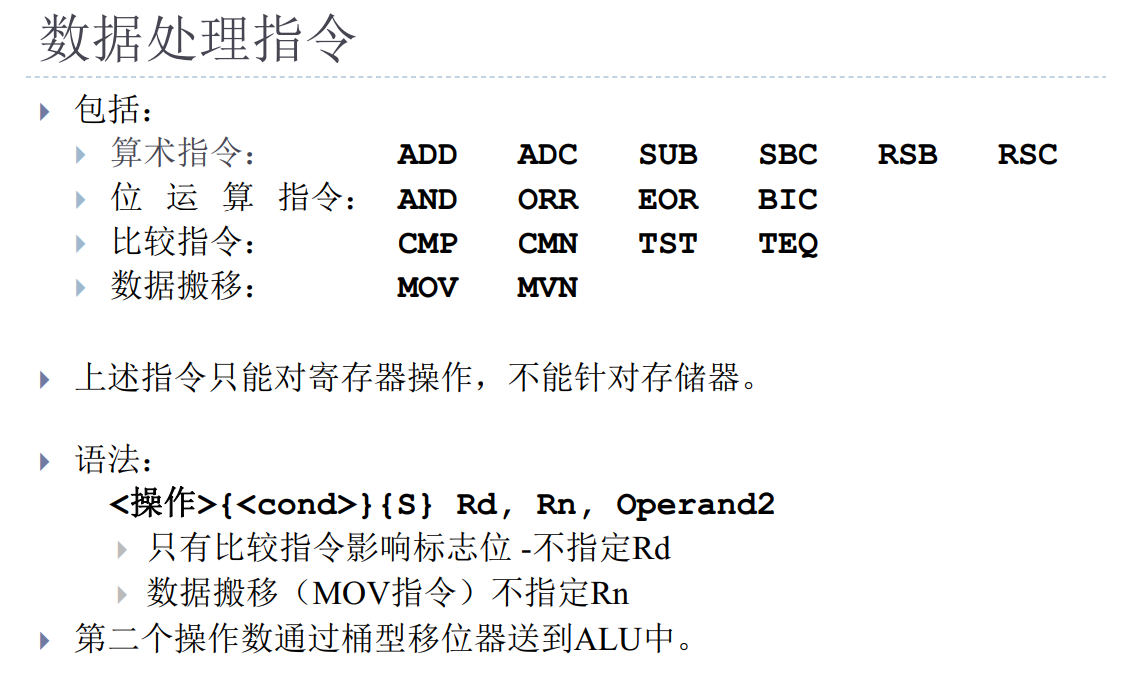

数据处理指令

Load/Store指令

跳转指令

程序状态寄存器处理指令:完成CPSR的管理

协处理器指令:完成CPU扩展功能的实现

异常产生指令

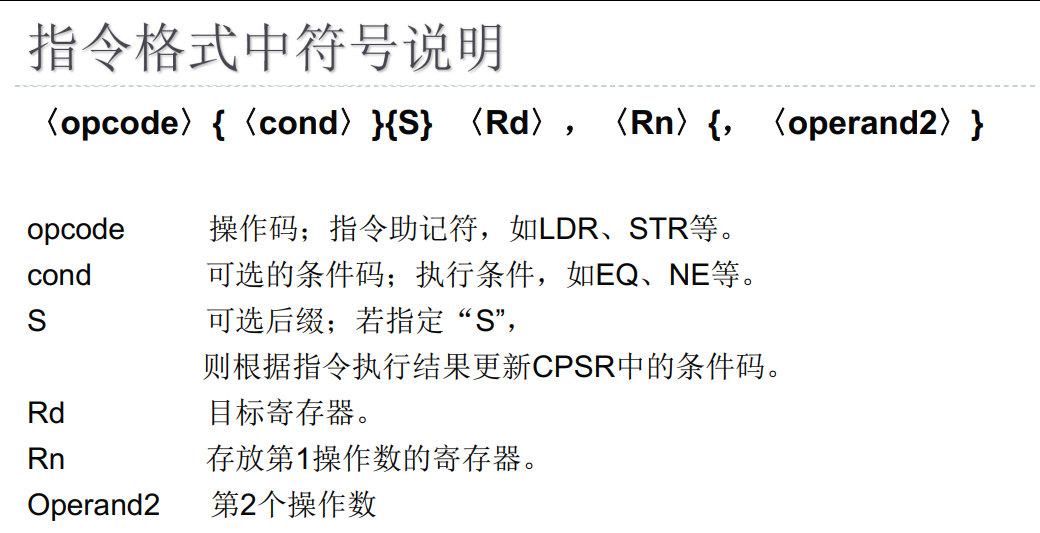

2、指令格式

3、数据处理指令

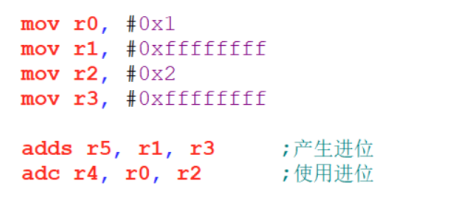

6、进位

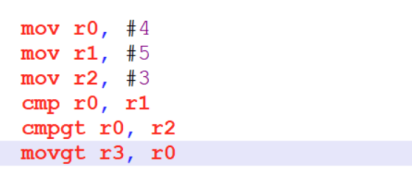

7、条件if

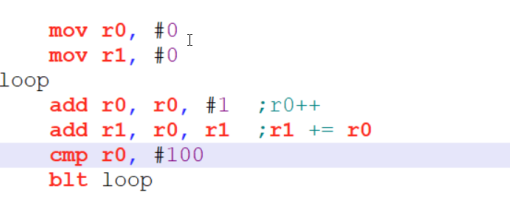

练习:求和(if+loop)循环

8、函数(难点)

立即数:一个数(或按位取反)循环右移2^n位后中所有的1能放进低8位中,#代表立即数

ldr sp,=0x40001000:将一个地址加载到寄存器中

函数调用的规则:

前四个参数用r0-r3传递,剩余的参数用栈传递(保护现场,恢复现场)

返回值在r0中

preserve8area reset, code, readonlycode32entrystartldr sp, =0x40001000mov r0,#1mov r1,#2import c_addbl c_addnopb startexport asm_add

asm_addstmfd sp!, {r4-r12,lr}add r0,r0,r1ldmfd sp!, {r4-r12,pc}end

int asm_add(int x, int y);int c_add(int a, int b)

{int sum = asm_add(a, b);return sum;

}5、PSR传送指令

swi #5软中断指令

swi后面的数范围是0-0xffffff

preserve8area reset, code, readonlycode32entryb startnopb deal_swinopnopnopnopnopdeal_swistmfd sp!, {r4-r12,lr}add r0,r0,r1ldmfd sp!, {r4-r12,pc} startldr sp, =0x40001000mrs r0,cpsr ;//程序状态寄存器(CPSR)的值读取到通用寄存器 r0bic r0,r0,#0x1f ;//清除 r0 的低5位(二进制 0b00011111),即 CPSR的模式位orr r0,r0,#0x10 ;//将 r0 的低5位设置为 0x10(二进制 0b10000),即切换到 用户模式msr cpsr_c,r0 ;//将修改后的 r0 值写回 CPSR的控制域(cpsr_c),完成模式切换ldr sp, =0x40000c00swi #5 ;//触发SWI中断(跳转到deal_swi)mov r0,#1mov r1,#2import c_addbl c_add ;//跳转到c_add函数处,并保存返回地址到lr寄存器nopb start ;//无条件跳转到start处export asm_add

asm_addstmfd sp!, {r4-r12,lr}add r0,r0,r1ldmfd sp!, {r4-r12,pc}end三、端口控制描述

1、端口控制描述

端口配置寄存器(GPACON-GPJCON):配置引脚的功能

端口数据寄存器(GPADAT-GPJDAT):读写数据

2、点亮led灯

#ifndef __LED_H

#define __LED_H#define GPBCON (*(volatile unsigned long *)0x56000010UL)

#define GPBDAT (*(volatile unsigned long *)0x56000014UL)

void led1_init(void);

void led1_on(void);

void led1_off(void);#endif

#include "led.h"

void led1_init(void)

{// 配置GPB5引脚功能为输出GPBCON &= ~(0x3 << 10);GPBCON |= (0x1 << 10);// 控制GPB5输出高电平 向GPBDAT第5位写1GPBDAT |= (1 << 5);

}

void led1_on(void)

{// 控制GPB5输出低电平 向GPBDAT第5位写0GPBDAT &= ~(1 << 5);

}

void led1_off(void)

{ // 控制GPB5输出高电平 向GPBDAT第5位写1GPBDAT |= (1 << 5);

}小tips:

volatile:易失性修饰符 读写值时都操作内存地址

配置1bit,一步完成

配置连续多个bit,两步完成,先清0,再置1

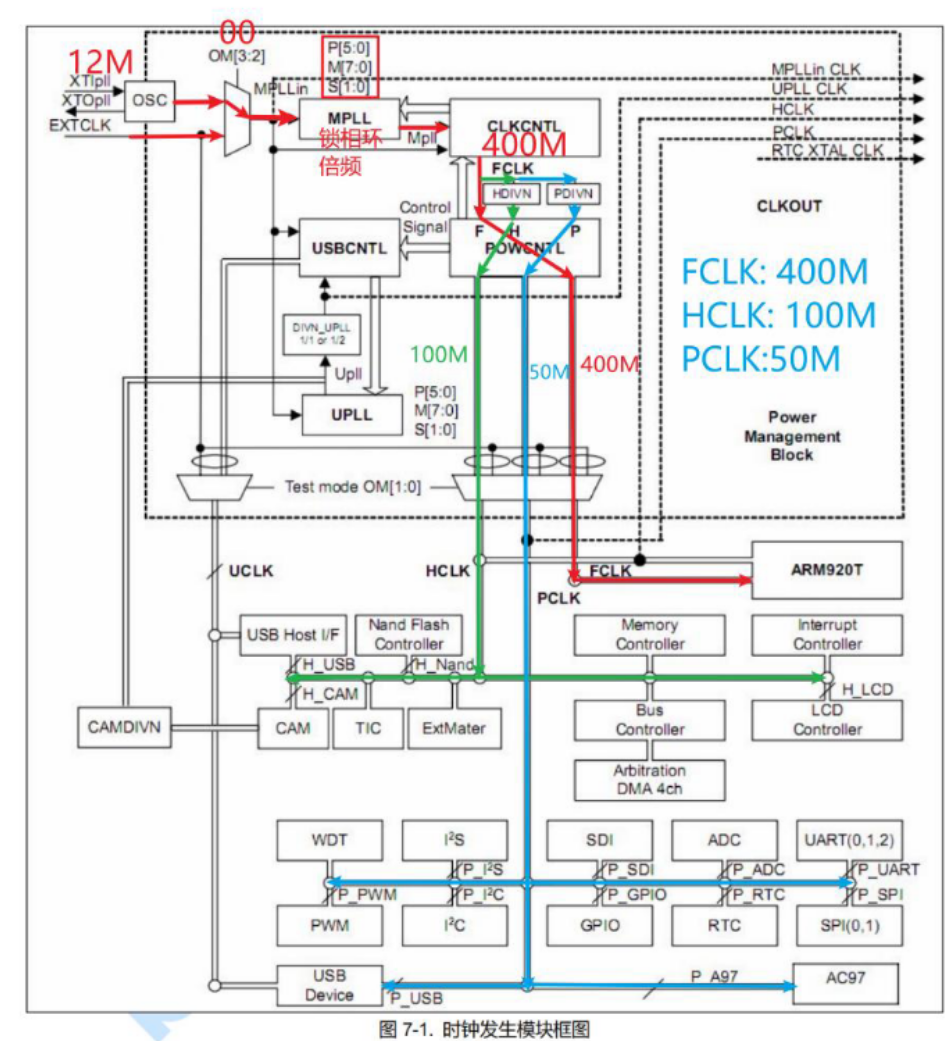

四、时钟管理

S3C2440A 包含两个锁相环(PLL:锁相环,倍频(提高频率))

一个提供给 FCLK、HCLK 和 PCLK,另一个专用于USB 模块(48MHz)

根据OM2 OM3选择时钟源(通过本次原理图,两个引脚接地,选择00模式)

代码

#ifndef __CLK_H

#define __CLK_H//#define MPLLCON (*(volatile unsigned long *)0x4C000004UL)

//#define CLKCON (*(volatile unsigned long *)0x4C00000CUL)

//#define CLKDIVN (*(volatile unsigned long *)0x4C000014UL)

//#define CAMDIVN (*(volatile unsigned long *)0x4C000018UL)void clk_init(void);

void clk_enable(unsigned char num);

void clk_disable(unsigned char num);#endif

#include <s3c2440.h>

#include "clk.h"

void clk_init(void)

{// 配置分频//CAMDIVN &= ~(1 << 9); //该位默认值为0CLKDIVN = (0x2 << 1) | (1 << 0);// 配置PLLMPLLCON = (127 << 12) | (2 << 4) | (1 << 0);

}void clk_enable(unsigned char num) //枚举

{CLKCON |= (1 << num);

}void clk_disable(unsigned char num) //枚举

{CLKCON &= ~(1 << num);

}五、中断

注意:

不支持中断嵌套

1、user模式(非特权)不能直接转换中断模式(特权),SVC模式可以直接切换中断模式

(特权优先级高于非特权)

2、函数的返回值,初始化栈

3、中断返回不一样

)

![《P4180 [BJWC2010] 严格次小生成树》](http://pic.xiahunao.cn/《P4180 [BJWC2010] 严格次小生成树》)

)