目录

1 DMA架构

1. 芯片架构图一览

2. AHB总线矩阵挂载

3. AHB1/APB1的桥和AHB1/APB2的桥

4. DMA1 和 DMA2 的区别

2 AHB总线矩阵

1 DMA架构

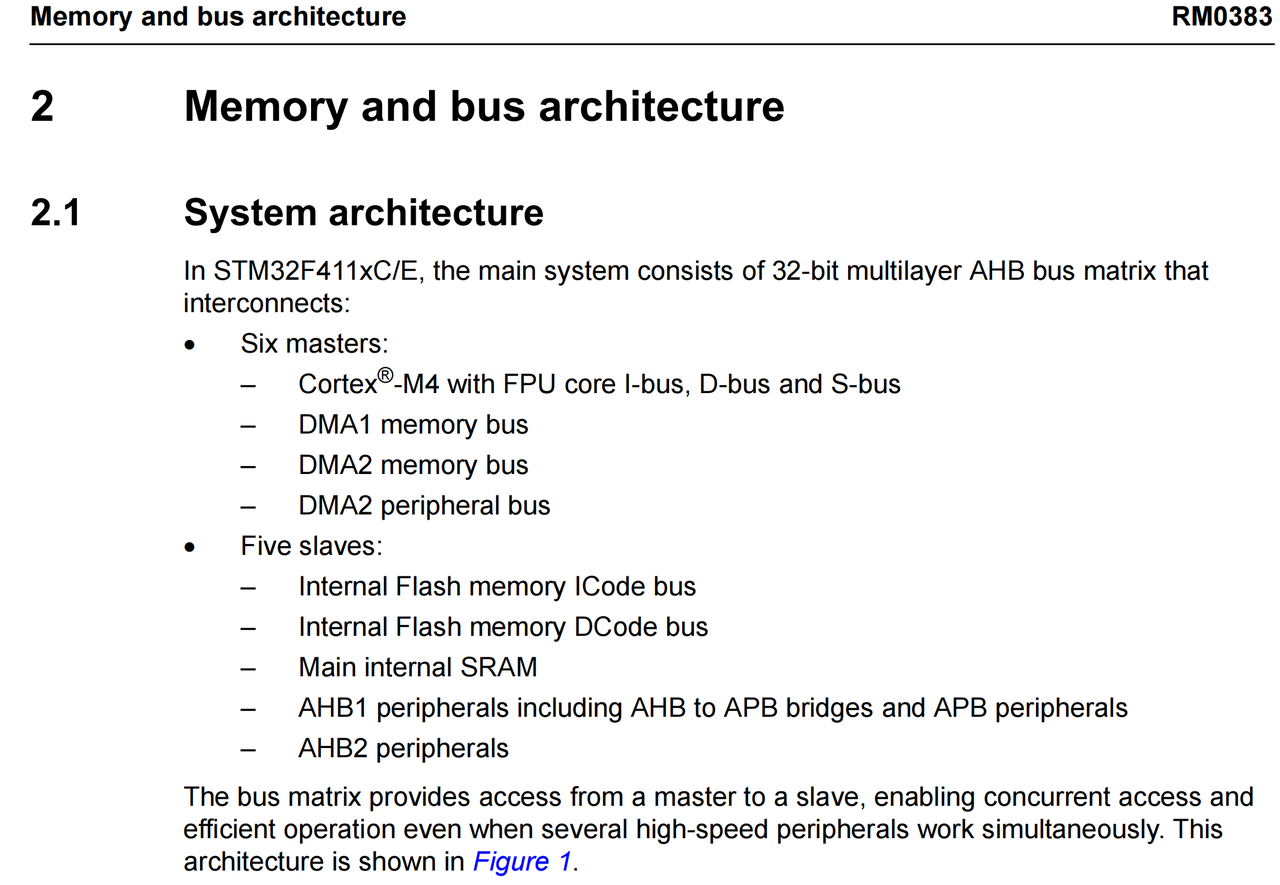

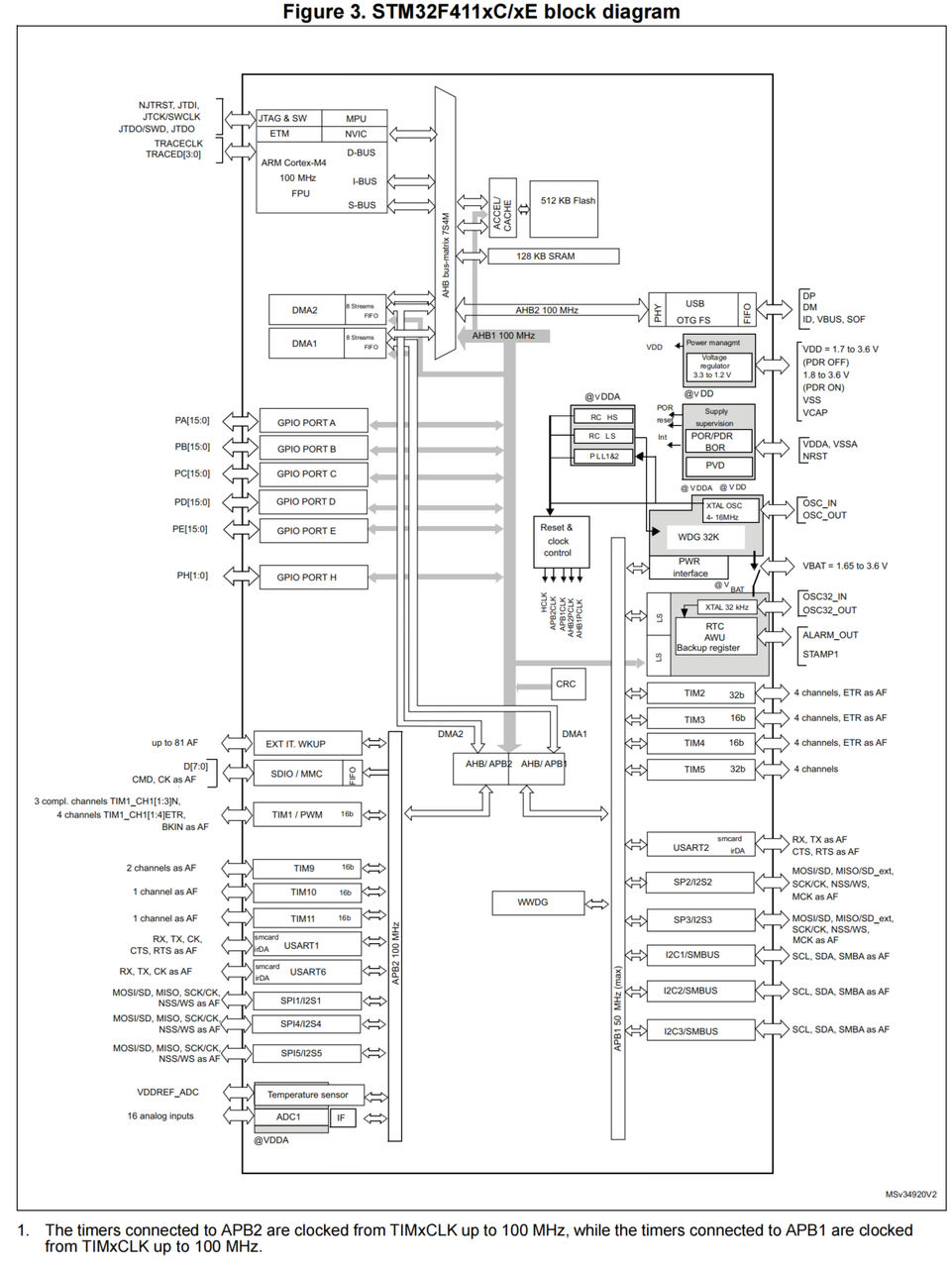

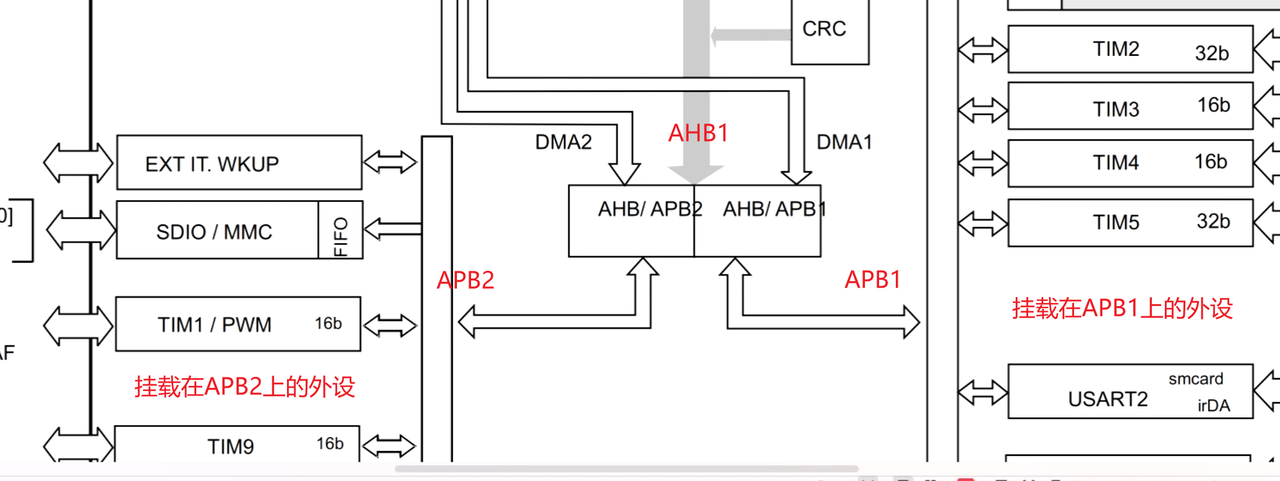

1. 芯片架构图一览

2. AHB总线矩阵挂载

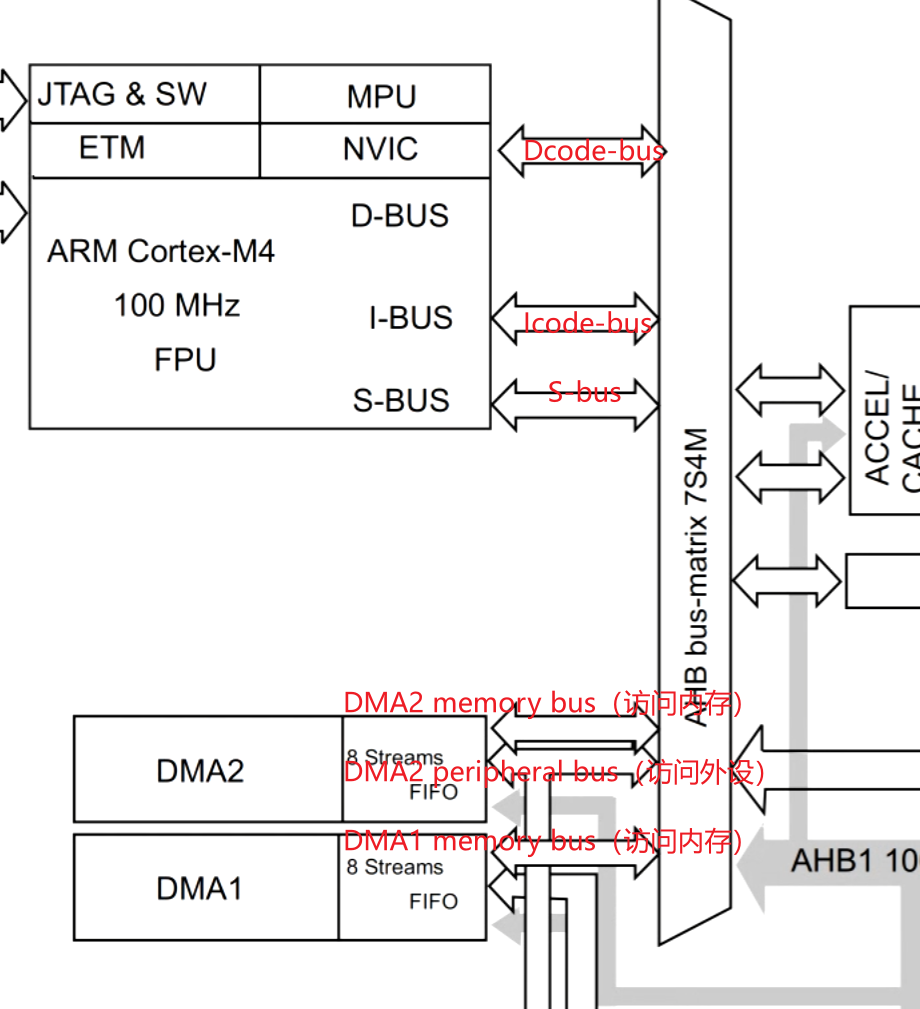

stm32F411 芯片的 AHB 总线矩阵上共挂载了 6 主 5 从

六主:

Icode-bus、Dcode-bus、s-bus(详情可见ARM内核结构)

DMA1 memory bus(访问内存)

DMA2 memory bus(访问内存)

DMA2 peripheral bus(访问外设)

五从:

-

Internal Flash memory ICode bus(接I-bus)

-

Internal Flash memory DCode bus(接D-bus)

-

Main internal SRAM(供给访问SRAM)

-

AHB1 peripherals including AHB to APB1 bridges and APB2 peripherals(AHB1总线,包括后面的AHB1/APB1的桥和AHB1/APB2的桥)

-

AHB2 peripherals(AHB2总线)

-

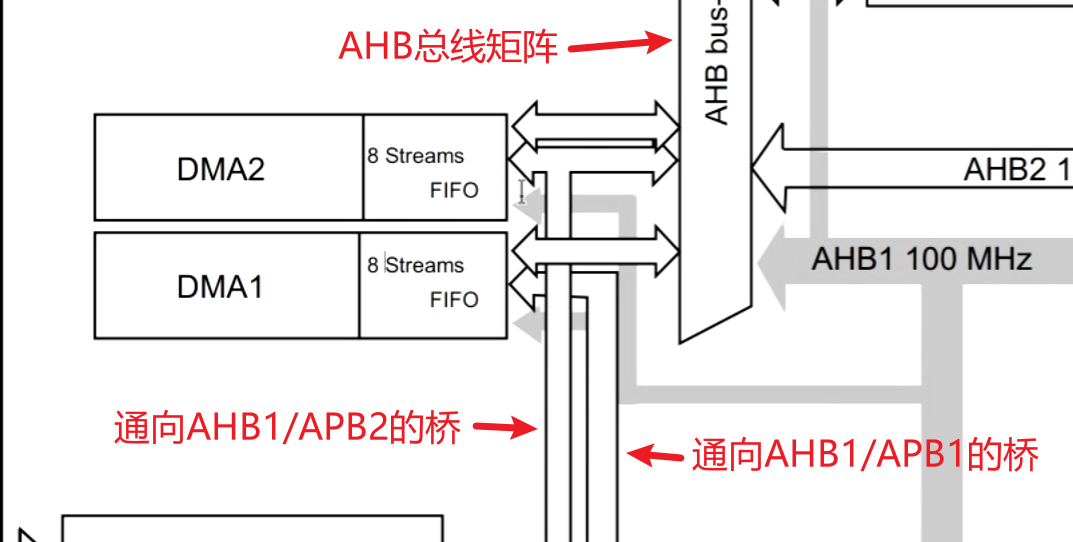

3. AHB1/APB1的桥和AHB1/APB2的桥

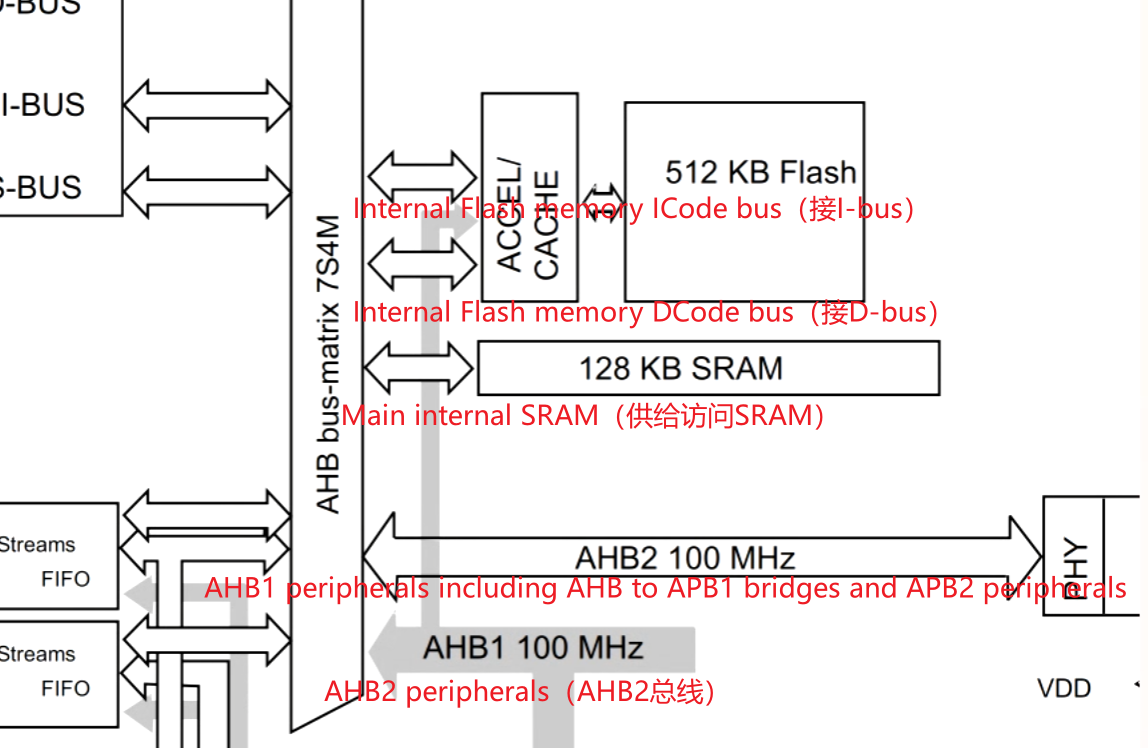

如图所示,AHB总线矩阵上有一个“从机”AHB1,因为AHB的速度是很快的,外设的速度不够快,为了正常读写,需要进行“降速”处理,所以就有了AHB1/APB2的桥和AHB1/APB1的桥来进行降速。

4. DMA1 和 DMA2 的区别

可以看到,DMA2 有两条 master 挂载在 AHB 总线矩阵上:DMA2 memory bus(访问内存)、DMA2 peripheral bus(访问外设)

DMA1 只有一条 master 挂载在 AHB 总线矩阵上:DMA1 memory bus(访问内存)

也就是说:DMA1 只能访问 APB1 总线上的外设,而 DMA2 可以访问更多外设

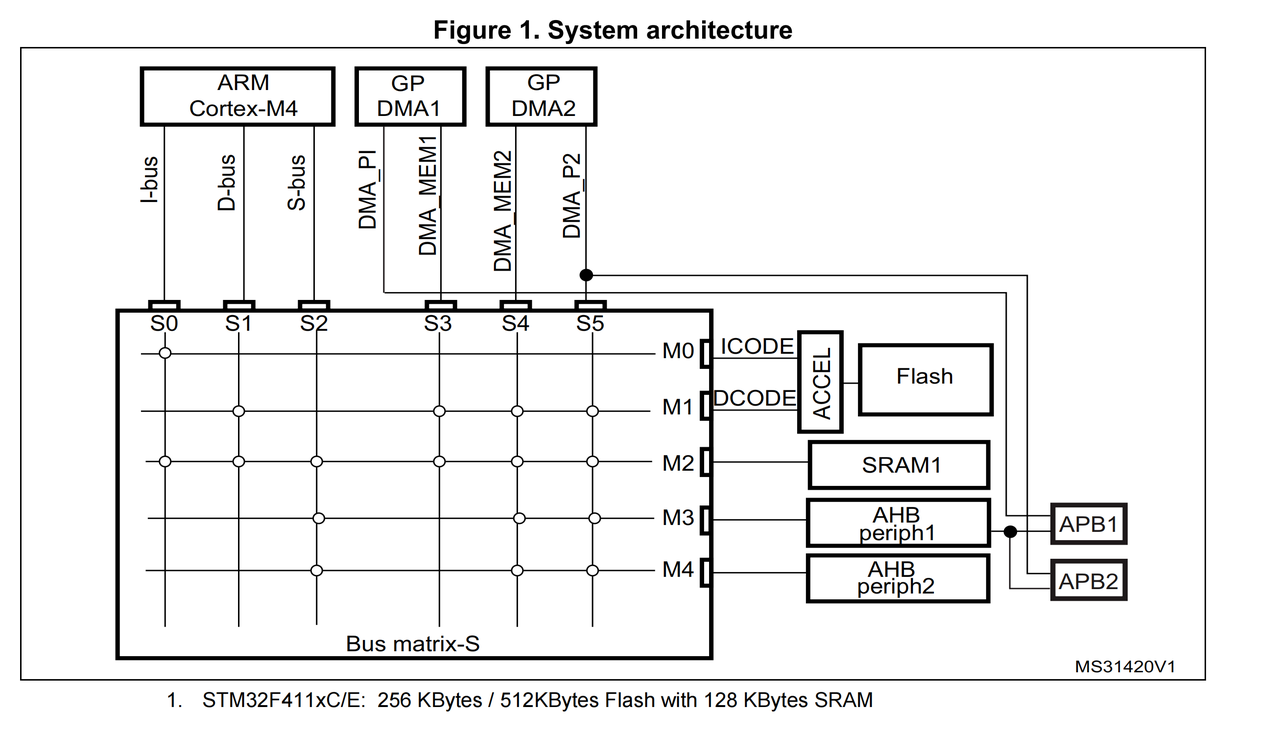

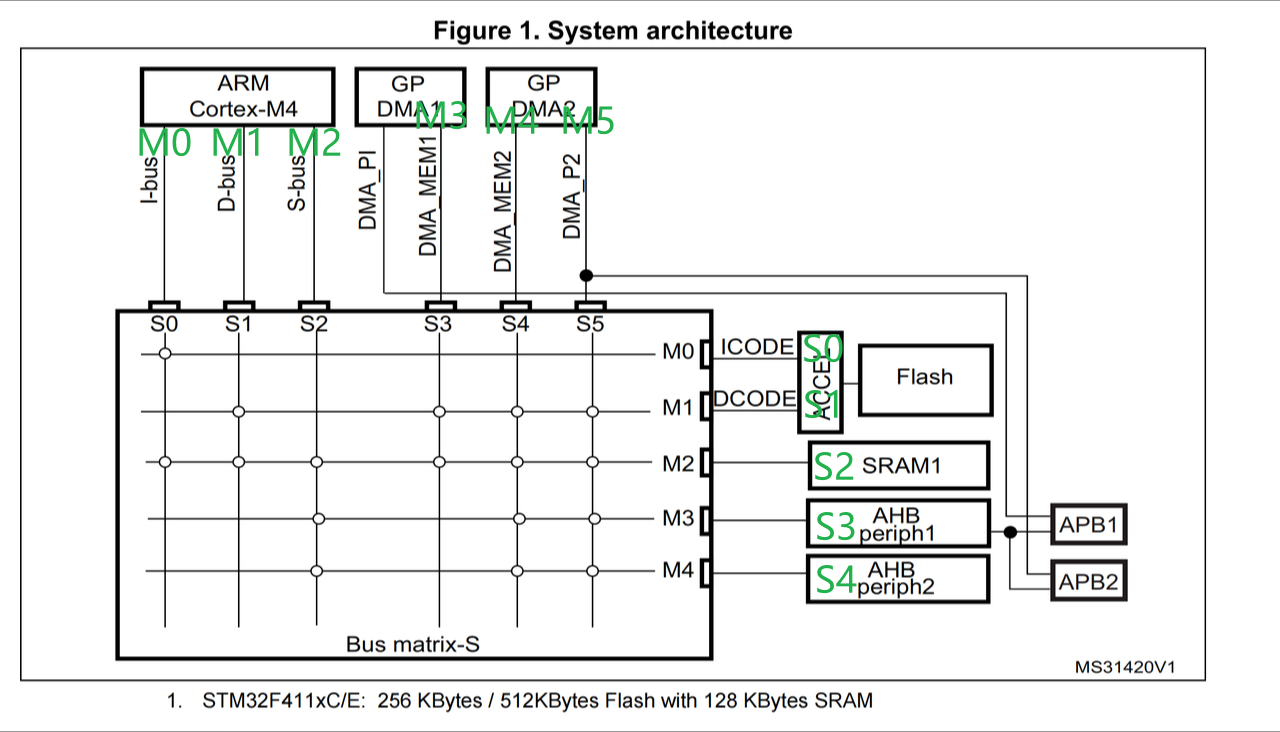

2 AHB总线矩阵

为什么总线矩阵中明明是 master 的位置标识的却是 S ?而 slave 的位置标识的却是 M?

一图解答:

图中总线矩阵上交叉线上的“小圆圈”代表这个位置“可以”连接起来。

关于系统总线架构的更多详情可见:ARM处理器总线架构解析:iCode、D-code、S-Bus与总线矩阵

由于其他总线与DMA关系不大,不在此赘述。

:刨根问底鸢尾花分类中的参数推理计算)