系列文章目录

文章目录

- 系列文章目录

- 前言

- 一、晶振主要参数

- 二、有源与无源区别

- 三、无源晶振

- 四、有源晶振

- 总结

前言

在硬件电路的设计中,晶振电路是必不可少的,它充当了整个电路心脏的作用。在这个晶振电路的设计中负载电容、电阻参数的选型是很重要的,选型失败不仅会波形失真,严重的芯片都无法工作。本文将从实验出发给出一种通用的配置。

一、晶振主要参数

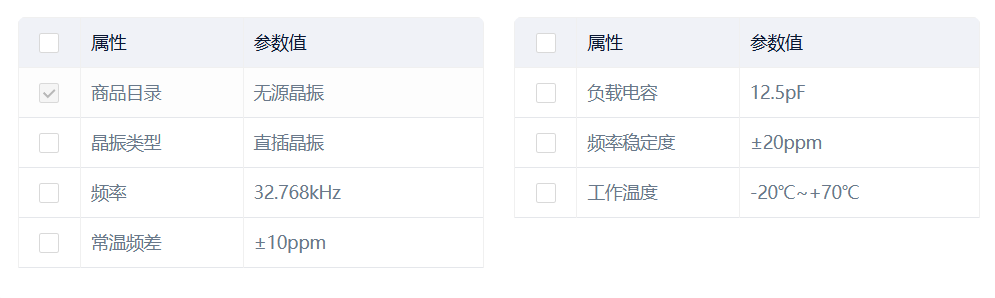

对于一款晶振主要参数如下

常温频差±10ppm

ppm 是 “parts per million” 的缩写,意为 “百万分之一”。在晶振参数中,±10ppm 表示在规定的工作温度范围内晶振的实际输出频率与标称频率之间的偏差范围,不超过标称频率的百万分之十。

若标称频率为 1MHz(1,000,000Hz),则频率偏差范围为 ±10Hz(1,000,000×10/1,000,000),实际频率在 999,990Hz 到 1,000,010Hz 之间。

负载电容12.5pF

负载电容(Load Capacitance,通常用CL表示)是指晶振在振荡电路中,从晶振两端看进去的总等效电容值(单位为皮法 pF)。它并非晶振自身的电容,而是由电路中外部电容(如振荡电路的匹配电容)、分布电容(PCB 布线、元件引脚等寄生电容)共同构成的总电容。12.5pF 表示该晶振正常工作时,需要外部电路提供的总等效负载电容为 12.5pF。

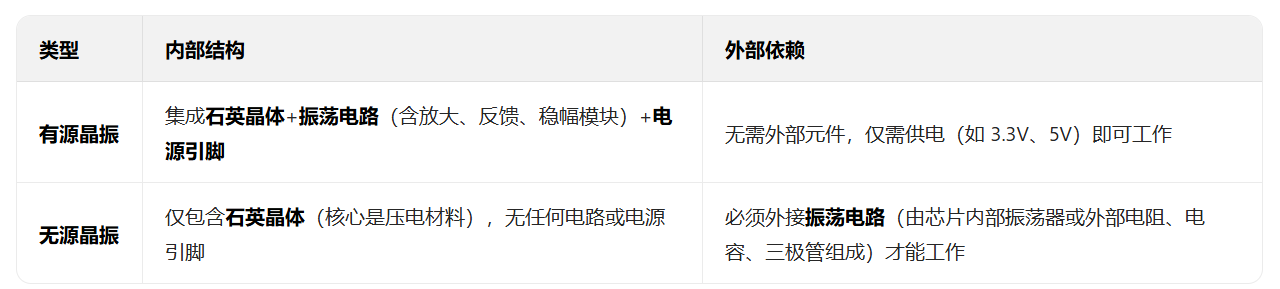

二、有源与无源区别

晶振分为有源和无源两种,区别如下

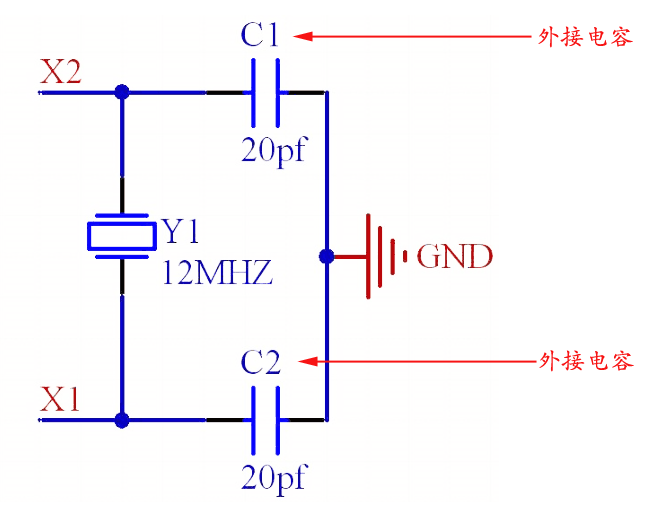

三、无源晶振

无源晶振一般是两个引脚,无方向之分,两个引脚接入芯片的OSC_IN与OSC_OUT引脚就可以工作了。一般电路设计如图所示。

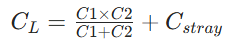

按前面介绍可得出外接电容(通常为两个对称的电容,C1 和 C2)来匹配 12.5pF 的负载电容,公式如下:

其中,Cstray 为分布电容(通常约 2~5pF,由 PCB 布线决定)。C1=C2从而能计算出C1=C2≈20pF。

一般无源晶振的产生的波形大多为三角波,频率准确性有限,所有对于精密电路都是使用有源晶振。

四、有源晶振

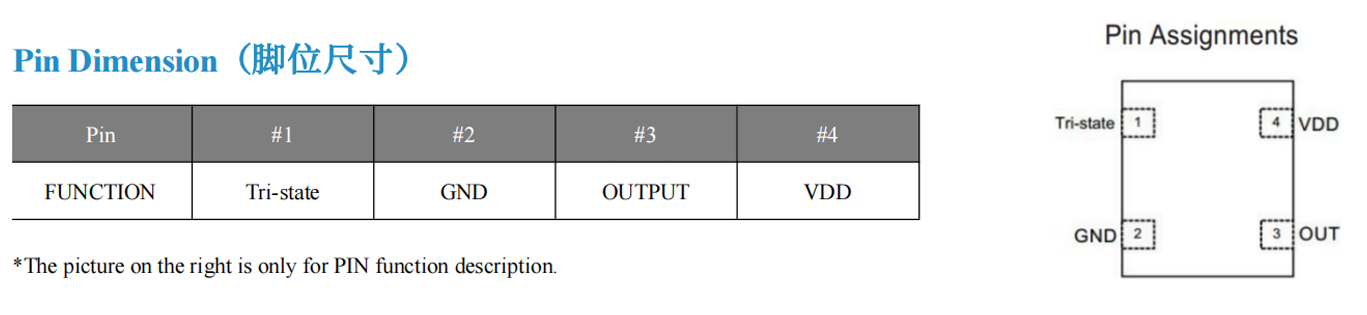

有源晶振一般是4个引脚,大多是表贴型,如图

其中的Tri-state是使能引脚,接高电平或高阻态输出波形,接低电平不输出波形,一般不适应,设计中保持悬空(高阻态)。

其中的Tri-state是使能引脚,接高电平或高阻态输出波形,接低电平不输出波形,一般不适应,设计中保持悬空(高阻态)。

OUTPUT就是波形输出引脚,设计中该引脚接入芯片的OSC_IN,芯片的OSC_OUT悬空。

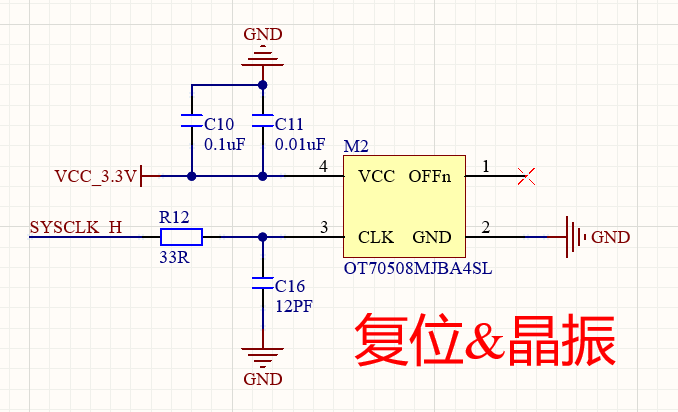

设计如图所示

其中的C16就是CL(负载电阻),R12为负载电容,有源晶振无需电容并联,直接CL=C16+Cstray即可。

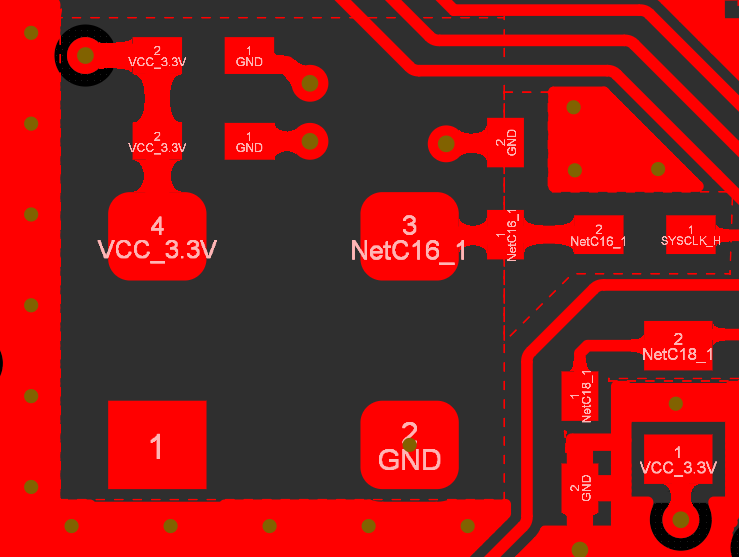

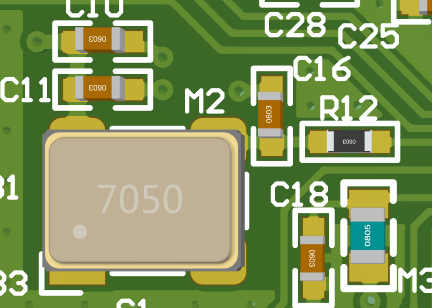

AD电路设计如图,顶层晶振电路周围围绕地铜,四周打上过孔与内电层或底层地铜形成良好连接,晶振电路内部不要铺铜,避免干扰高频电路,晶振电路底下(内电层或底层)最好的铺满大片铜皮,形成良好的电磁屏蔽。另外最好不要在晶振电路的内部和底下走线,保持铜片连续和避免信号干扰。

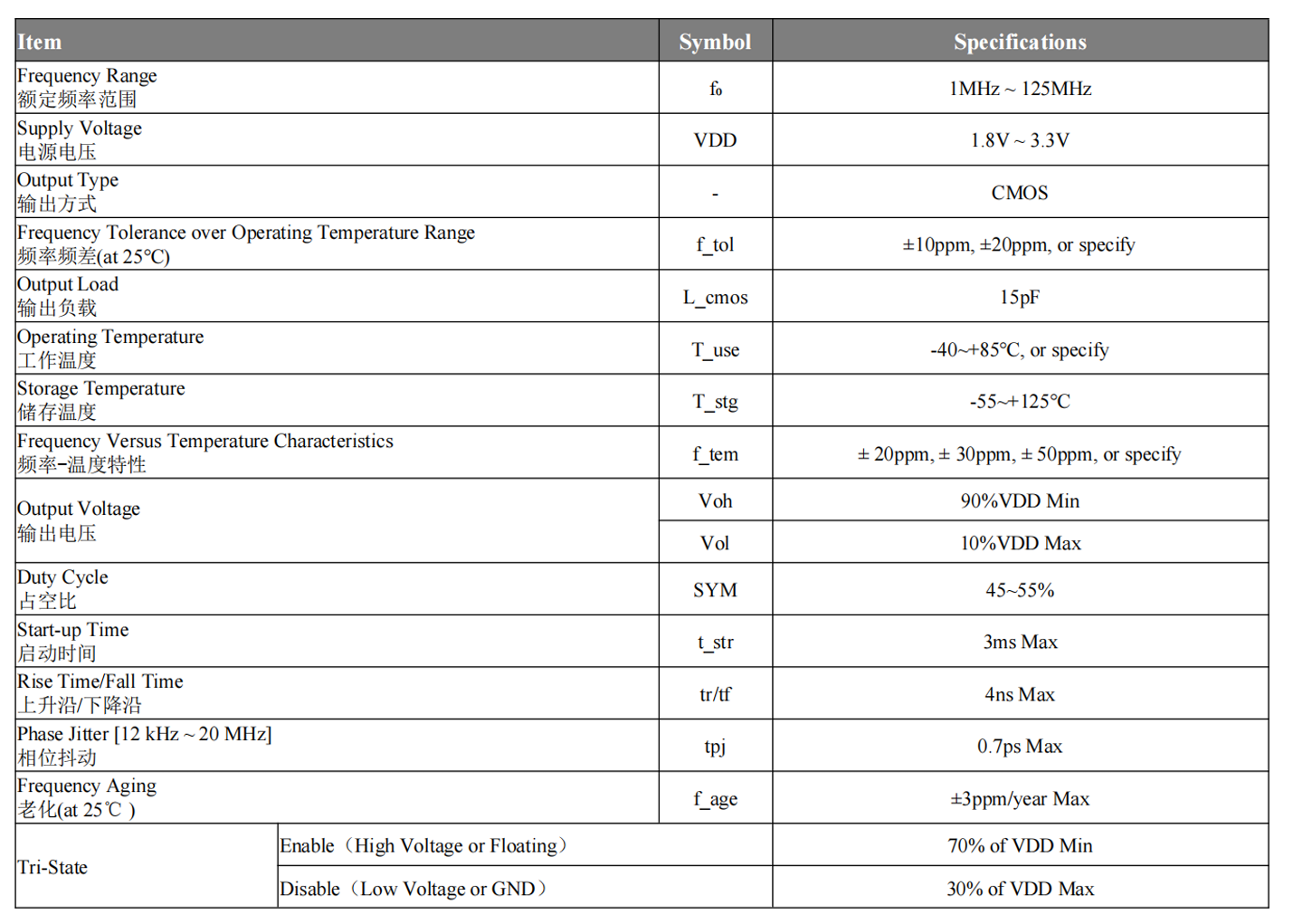

这是该电容的具体参数图

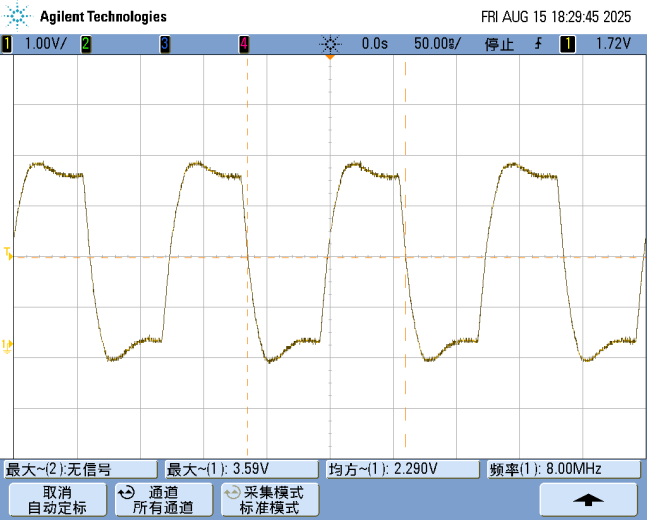

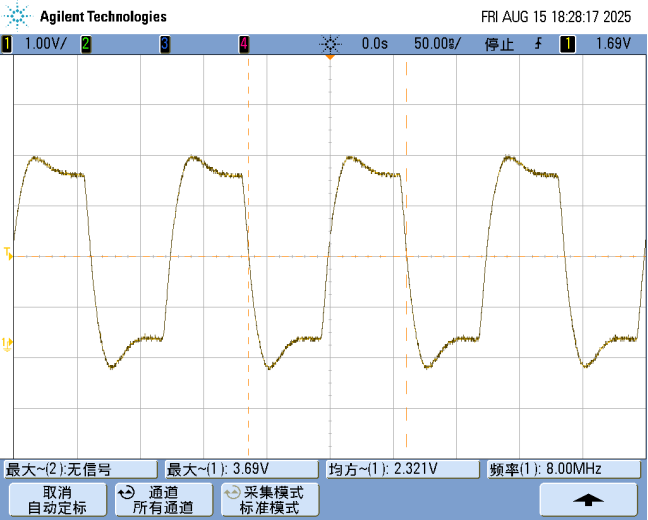

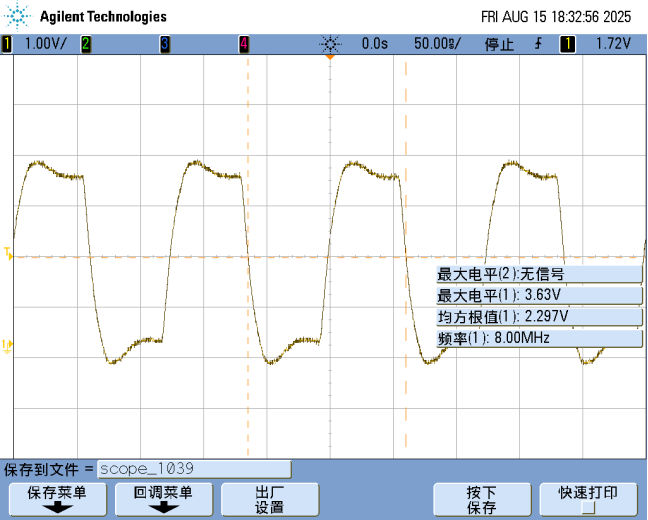

下面按照该电路设计,改变C16和R12的值,依靠示波器寻找最合适的搭配,大家可以仔细对比。

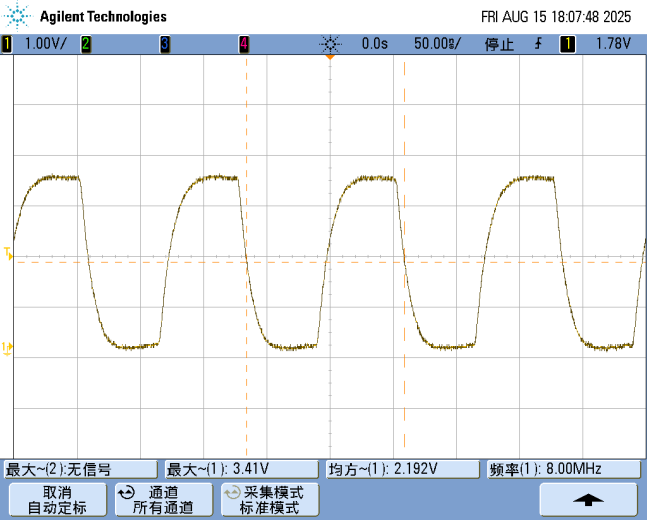

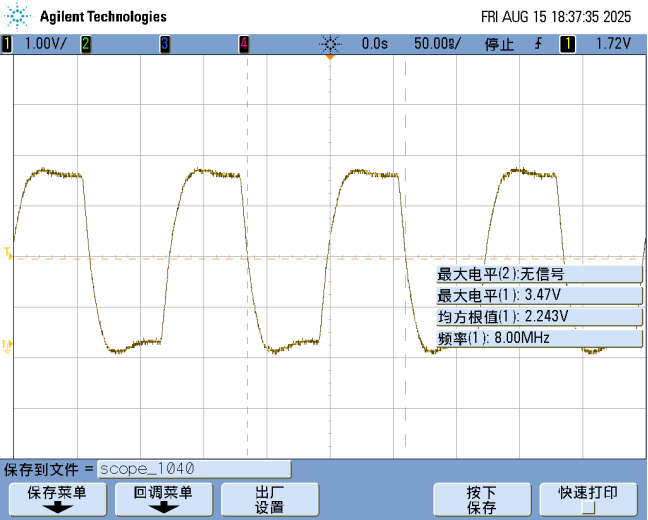

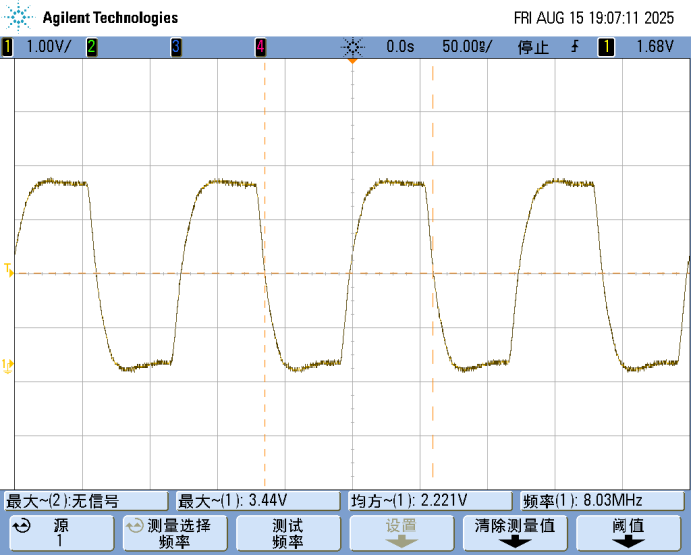

负载电容0PF、负载电阻0R

负载电容12PF、负载电阻0R

负载电容15PF、负载电阻0R

负载电容12PF、负载电阻33R

负载电容15PF、负载电阻10R

负载电容15PF、负载电阻20R

最后我选择了C16=15PF,R12=20R的设计,因为比较之下这是在上升时间短的要求下几乎无超调的一款设计,最贴近理论方波。

总结

可以看出因为有源晶振自身具有起振电路在负载匹配的要求上不是那么苛刻,上面所有的波形都可以满足驱动芯片运行,可以按照我的设计图,查晶振手册,负载电容和手册规格相等或低几PF,复杂电阻保持为20R,这样几乎可以使用绝大多数硬件设备的时钟频率要求了。在设计时也尽可能的选择有源晶振。

多说一句,一般MCU内部也具有内部晶振,不过要说的是这个内部晶振频率非常不准,如果使用内部晶振会导致USART通讯失败,这种失败还不好察觉,因为失败的原因是时钟不准导致的波特率和设定的不符,从而收到乱码,尽量不要使用内部晶振工作。

|轻量化 MobileNetV2 高光谱分类)

的进化之路)

)

)