如果你对 FPGA 有些了解,大概知道它的意思是“可编程逻辑器件”,可以把写好的逻辑电路(通常是 Verilog/VHDL)通过工具综合、布局布线、烧写进去,让一块芯片变成“你想要的电路”。

但如果我告诉你,现在有个开源项目,能让你:

🧩 在一个 FPGA 里“模拟出”另一个 FPGA

🔧 自己设计一整套 FPGA 架构:LUT、开关矩阵、配置链、IO 结构,全由你说了算

💡 最后甚至还能用自己的工具链,生成 bitstream 文件,像真的 FPGA 一样配置运行

你会不会觉得这太“套娃”了点?

这不是虚构,也不是概念,而是一个真正存在的开源项目——OpenFPGA。

OpenFPGA 是什么?

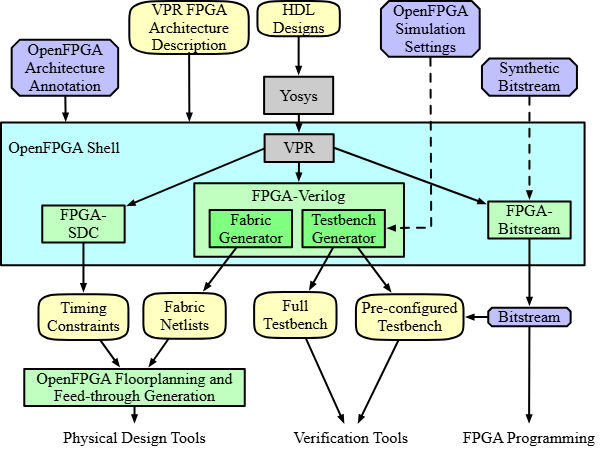

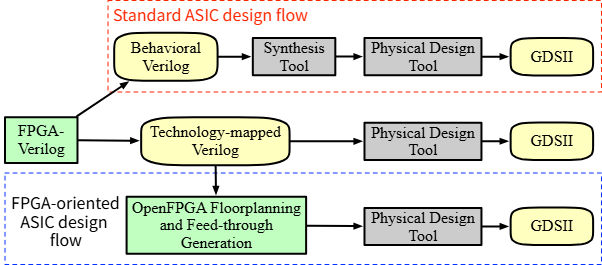

OpenFPGA 是一个由美国犹他大学(University of Utah)开发的开源平台,用于:

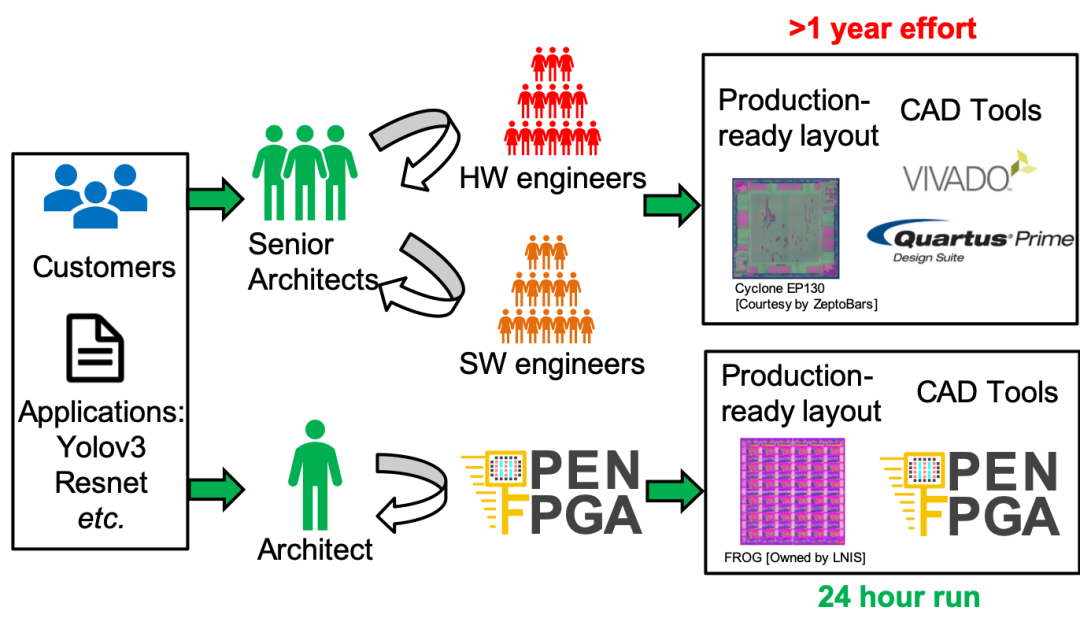

快速构建、验证、测试和优化可定制的 FPGA 架构。

说白了,它提供了一整套工具链,让你可以像拼乐高积木一样,去“搭”出你自己想象中的 FPGA 架构,并且:

自动帮你生成 Verilog 实现

生成 bitstream 加载配置

集成仿真、综合、布局布线流程

支持在真实 FPGA 或仿真器中运行验证

更重要的是,OpenFPGA 本身就是开源的,你可以把它用于教学、研究、探索架构、甚至 tape-out 前的原型验证。

它能做什么?

用一句话总结:

让你从“用 FPGA 写逻辑”→“自己设计一颗 FPGA”。

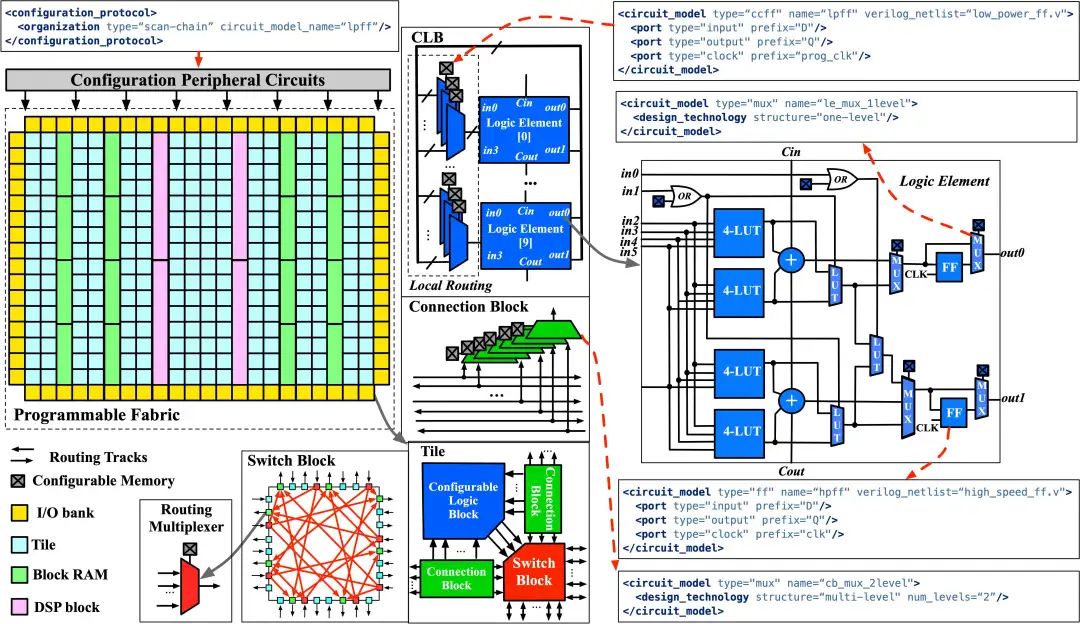

更具体地说,它支持你:

能力 | 描述 |

|---|---|

🎛️ 架构定义 | 自己定义 LUT、MUX、交叉开关、布线资源 |

📐 自动生成 RTL | 从架构描述出发生成 Verilog 模块 |

🛠️ 搭建配置链 | 包括 SRAM 控制、bitstream 加载逻辑 |

📦 编译用户电路 | 用 VTR 工具链将用户模块映射到你的软 FPGA 架构上 |

💡 Bitstream 控制 | 输出配置数据,加载到 FPGA 架构中驱动运行 |

🔄 验证工具 | 提供仿真、资源分析、可视化接口等 |

最终你会得到一个在真实 FPGA 上运行的 “可配置逻辑网络”,也就是你自己的“软核 FPGA”。

🤔 它和我们平时用的 FPGA 有什么区别?

项目 | 普通 FPGA(如 Vivado + Zynq) | OpenFPGA |

|---|---|---|

架构 | 固定(由芯片厂预定义) | 你说了算 |

工具链 | 专有(Xilinx/Intel) | 开源(Yosys + VTR + OpenFPGA Flow) |

使用方式 | 写 Verilog 实现功能 | 先设计架构、再烧进“功能” |

适用范围 | 产品开发 | 教学、研究、架构探索、原型验证 |

Bitstream 格式 | 加密、私有 | 自定义、开源可分析 |

你可以把 OpenFPGA 理解为“FPGA 架构设计的实验室”: 不再是用别人造好的芯片,而是自己动手定义一套“芯片的内核”,并用代码亲自搭出来。

为什么要做这样的项目?

这个项目的核心目标其实很清晰:

探索更多样的 FPGA 架构设计(比如不同尺寸的 LUT、异构逻辑块)

做科研/芯片前验证:不确定某种布线方式是否高效?先在 OpenFPGA 上验证一下

教学用具:让学生“看见并理解”一个 FPGA 的完整内部结构和工作机制

构建自定义 FPGA Overlay:比如把这套软核嵌进更大的 SoC 中当作自定义协处理器

所以它的定位不是要替代 Xilinx/Intel 的 FPGA,而是:

“给你一张白纸和一套画笔,让你画出自己理解的 FPGA 架构。”

你不仅能跑 HDL,还能造 HDL 运行的平台,真正从“使用者”进化为“创造者”。

传送门

项目地址:https://github.com/lnis-uofu/OpenFPGA

配套架构设计手册:https://docs.openfpga.org/

推荐结合 VTR 项目一起食用:https://github.com/verilog-to-routing/vtr-verilog-to-routing

如果你也想:

搭建自己的软核 FPGA?

理解 FPGA 背后的世界?

或者在下次答辩/讲座/面试时秀一波底层知识?

OpenFPGA 不适合高性能产品,但绝对是探索 FPGA 架构的神器!

)