文章目录

- 概述

- 配置图元素说明

- RCC

- HSI/LSI/HSE/LSE

- AHB 和 APB

- SYSCLK 和 HCLK

- Mux 多路复用器

- Prescaler 预分频器

- PLL 锁相环

- PLL 配置寄存器

- 时钟物理源

- 内部时钟和驱动

- 无源晶振和驱动

- 有源晶振和驱动

- MCO 时钟信号

- 音频时钟配置

- 晶体振荡器?

- 外部时钟源类型

- RCC 如何选择

- 旁路模式-有源晶振

- 旁路模式-时钟信号

- 频率冲突和计算

- 时钟给谁用?

概述

阅读本文的内容后,我们便可以真正地去读懂STM32时钟配置图的全部内容,打开理解STM32时钟树的第一道大门。

1、逻辑电路符号(如PLL、Mux等)说明、名词(HSI/LSI/HSE/LSE、AHB/APB、SYSCLK/HCLK)说明等;

2、Crystal/Ceramic Resonator、BYPASS Clock Source、有源晶振、无源晶振、旁路模式、晶振模式等概念及其关联。

3、有源晶振/无源晶振管脚、电路图设计和分析。

4、了解频率自动计算和频率冲突问题。

@History

202306 此时,我应该连半个嵌入式程序员都算不上,虽然基于STM32+FreeRTOS搞过半年多的嵌入式编程,但是环境都是别人搭建的,就连GPIO配置、OS配置等都是别人帮助我搞得,我充其量就是完成了一次C程序设计和代码编码。即使是在参与了许多嵌入式项目后的,我依然对于嵌入式编程,都是一知半解,算不上入门。借着学习 STM32Cube 的机会,开启一段新里程,加深个人对嵌入式开发的理解。我通常的学习路径是,粗实践-细理论-细实践。本文,MX时钟树解读就是我细理论的第一战。

配置图元素说明

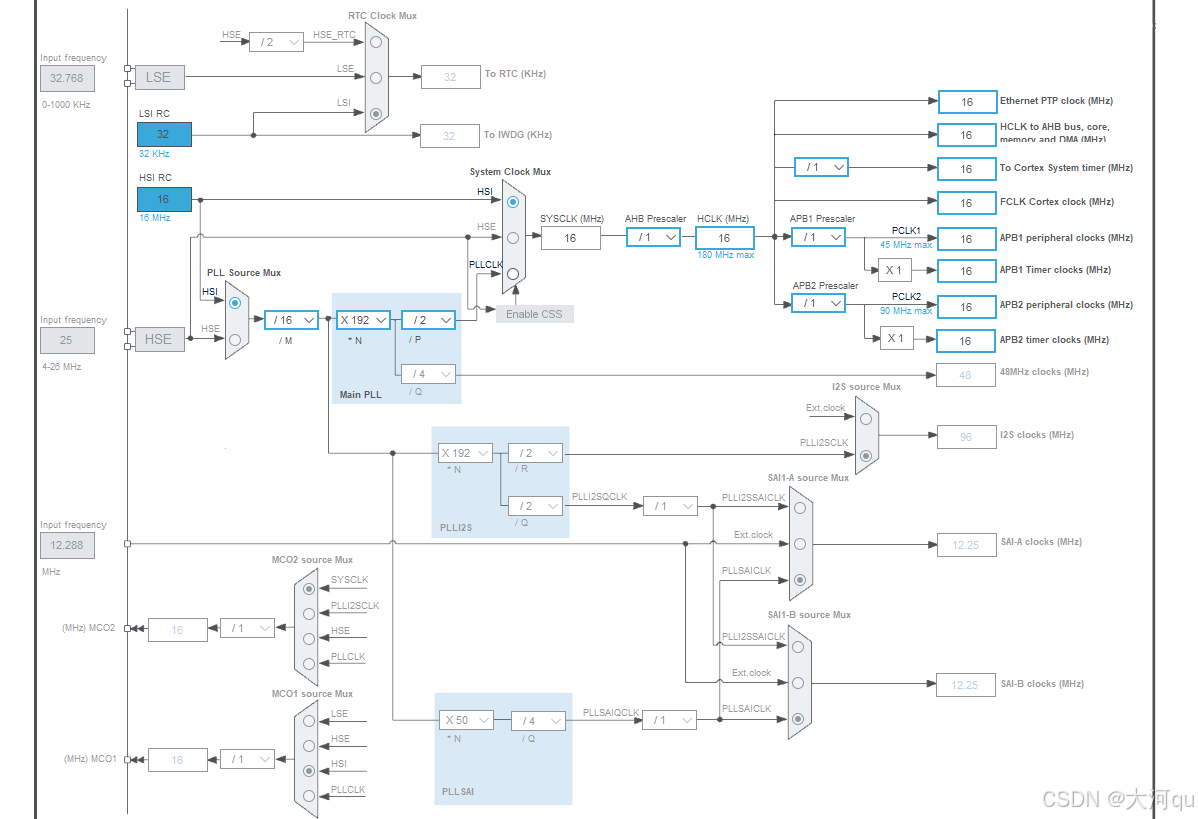

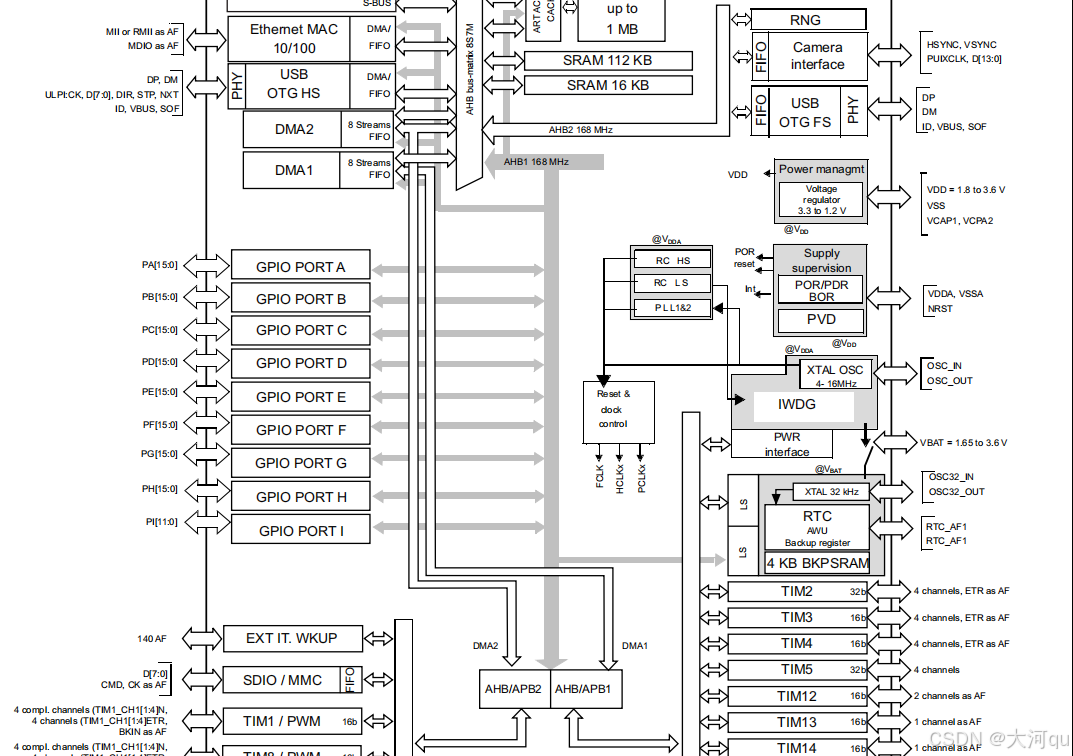

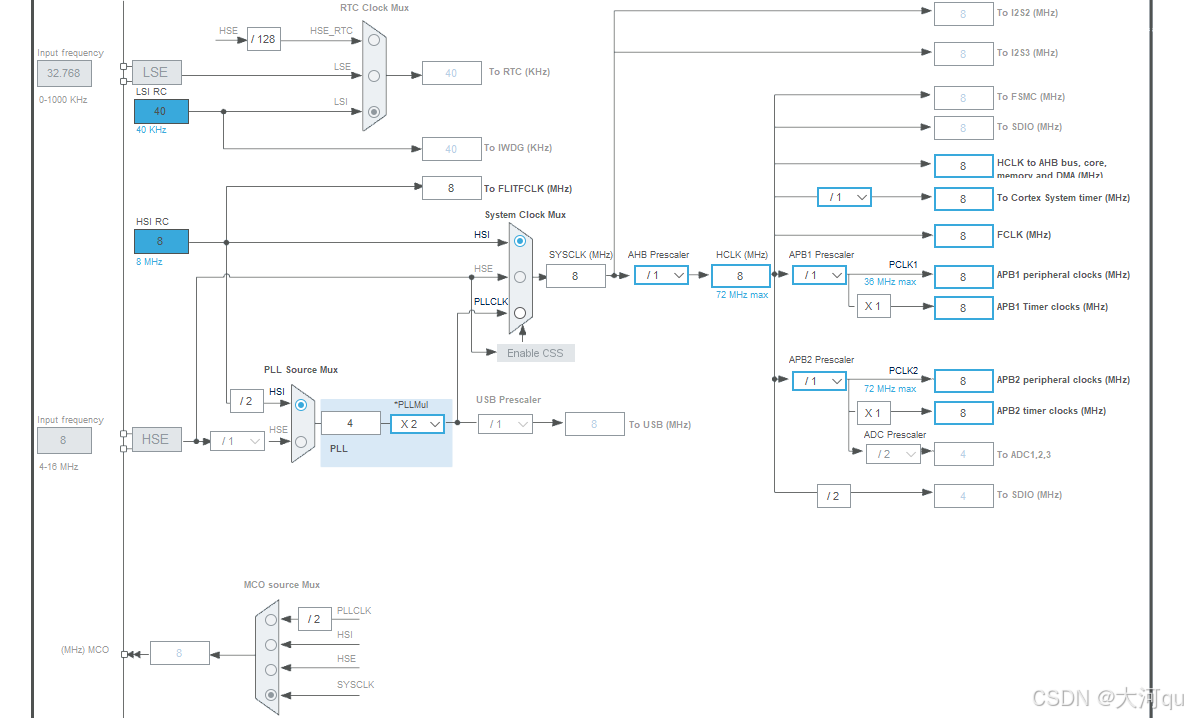

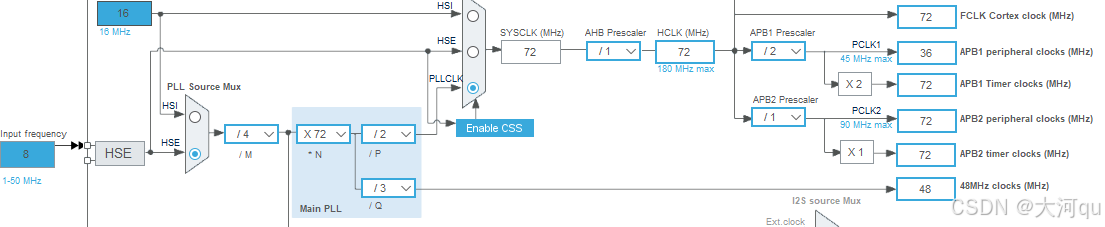

要实实在在的看懂时钟配置图,第一步,要理解时钟图中的各个名称或缩写名称的含义,理解图中的器件的功能。我们新建一个基于STM32F427的MX工程,默认情况下的时钟配置如下图,STM32F427ZIT6,

RCC

RCC 是 Reset and Clock Control(复位与时钟控制器) 的缩写,控制外设的硬件复位,为CPU内核、外设提供稳定的时钟信号。

HSI/LSI/HSE/LSE

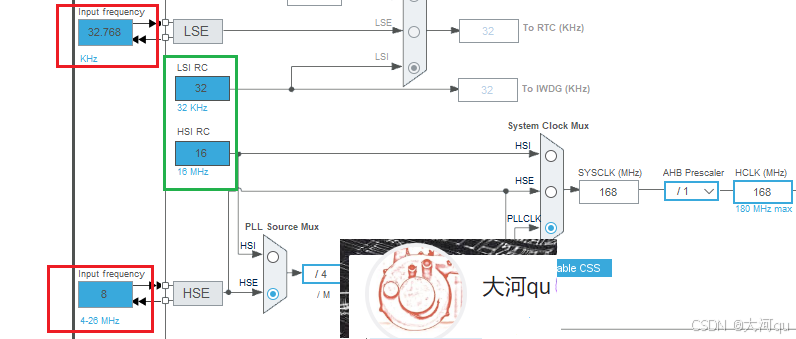

HS和LS,是High Sped 和 Low Speed 的缩写,这些通过上图都可以意识到。那么I和E呢?其实这里它们分别是Internal和External。即内部高低速时钟和外部高低速时钟。内部高低速时钟,不需要任何外部电路,不涉及GPI配置过程。相关标识如下图红色和绿色框。

LSE(低速外部晶振):LSE是一种低频率的外部晶振,通常使用 32.768KHz 的频率。它主要用于提供低功耗时钟,例如RTC(实时时钟)和低功耗模式中的时钟源。LSE适用于需要长时间稳定运行的应用,如实时时钟和定时器。

HSE(高速外部晶振):HSE是一种高频率的外部晶振,通常使用 4MHz 到26MHz的频率。它用于提供高速时钟源,供微控制器的内部逻辑和外设使用。HSE适用于需要高性能和高速通信的应用,如高速串行接口(例如SPI、I2C、USART)和高速计时器。

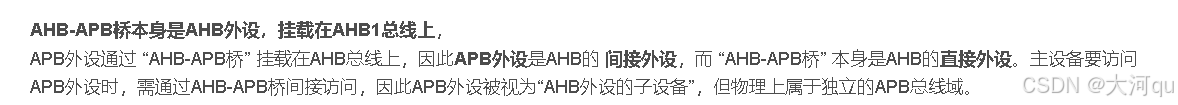

AHB 和 APB

在STM32微控制器中,AHB(Advanced High-performance Bus,高级高性能总线) 和 APB(Advanced Peripheral Bus,高级外设总线) 是 片上总线架构 的核心组成部分,用于连接CPU、内存和外设,实现数据传输。AHB专注于高带宽、低延迟,APB专注于低功耗、外设兼容性。

AHB是STM32的系统主干总线,连接CPU、内存(SRAM/Flash)和高带宽外设,设计目标是高吞吐率、低延迟,支持突发传输(Burst Transfer)和流水线操作。仔细观察是时钟图和阅读数据手册,便可以窥探一二。关于,AHB和APB上外设的挂载,我们在后续文章中会继续谈。这里先不多说了。可以先提一点,

最累的是AHB1,下图中的灰色实心线表示了与它相关的设备,

SYSCLK 和 HCLK

SYSCLK(System Clock,系统时钟)

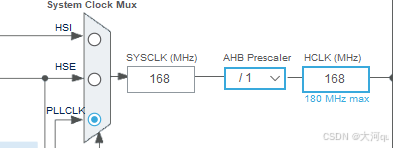

它是STM32的主时钟源,是CPU(Cortex-M内核)运行的基准时钟,也是其他所有时钟(如HCLK、PCLK)的源头。其频率直接决定了CPU的运算速度,如168MHz SYSCLK对应CPU最大168MIPS的处理能力。事实上SYSCLK类似于我们常说的主频的意思,该时钟驱动CPU的指令执行。即在CubeMX中,通过 Clock Configuration 界面的 System Clock Mux(系统时钟多路选择器)选择SYSCLK的来源,默认优先使用PLLCLK,此时频率最高,性能最优。

HCLK(AHB Clock,高速总线时钟)

HCLK高速总线的时钟,由SYSCLK经过 AHB Prescaler(AHB分频器) 分频得到,分频系数可配置为1、2、4、8、16、64、128、256、512(默认1分频,即HCLK = SYSCLK)。该时钟为连接在AHB总线上的高带宽外设提供时钟,同时也是CPU的“总线接口时钟”(CPU通过AHB总线访问内存和外设)。再直白点说就是,驱动AHB总线及外设:如SRAM、Flash、DMA控制器、SDIO、ETH、Timer等需要高带宽的外设。

Mux 多路复用器

在时钟配置图中,我们可以看到多个Mux逻辑电路符号,

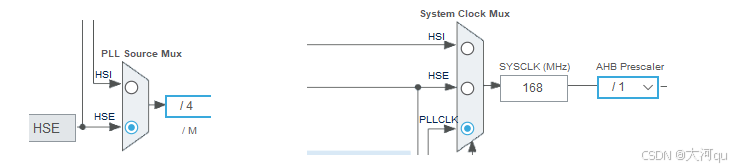

Mux 是 Multiplexer(多路复用器) 的缩写,可以认为它是一种电子选通开关电路,可从多个输入信号中选择一个,并将其输出到单一通道。这里以两个最主要的Mux为例,它们的功能介绍大约如下,PLL Source Mux(PLL源多路选择器) 是一个硬件开关,用于选择PLL的输入时钟源(即“喂给”PLL的原始时钟)。System clock Mux(系统时钟多路选择器) 是STM32时钟树的“总开关”,用于选择系统时钟(SYSCLK)的最终来源,直接决定CPU内核、内存和大多数外设的工作频率。

Prescaler 预分频器

美 /'pri:skeilə/ 预分频器。在STM32CubeMX的“Clock Configuration”(时钟配置)界面中,预分频器(Prescaler) 是降低时钟频率的核心组件,通过对输入时钟进行“分频”(除以某个整数),为不同外设提供匹配其最高工作频率的时钟信号。预分频器是STM32时钟树的“流量控制器”,确保高速系统时钟(如168MHz)能适配低速外设(如UART最高支持42MHz)。

PLL 锁相环

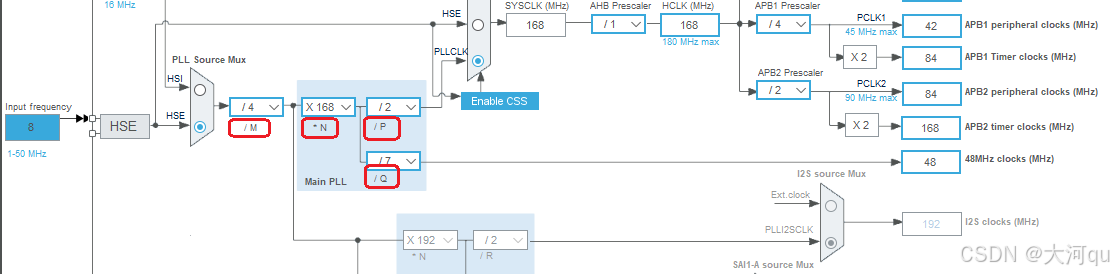

PLL(Phase-Locked Loop,锁相环) 是STM32中用于倍频/分频时钟的核心模块,可将低频时钟(如8MHz HSE)倍频至高频(如168MHz),供系统时钟和高速外设使用。

以STM32F427为例,其PLL输入频率,无论是使用HSI还是HSE,通常都要先分频处理。分频的核心目的是将原始高频时钟(HSI/HSE)降至PLL的输入频率范围(如2 MHz),保证PLL稳定工作。若原始时钟频率 恰好落在PLL输入范围内,则无需分频。

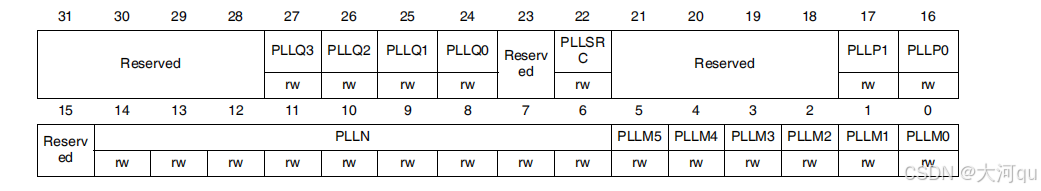

PLL 配置寄存器

当我首次注意到PLL锁相环的M、N、O、P、R时,稍微有点蒙,难道它们有什么特殊含义吗?

RCC PLL 配置寄存器 (RCC_PLLCFGR) RCC PLL configuration register

其实,这里的MNOP并没有特殊的含义,纯粹的是PLL寄存器字段的编号。如上寄存器位域分配表所示,

位 5:0 PLLM:

主 PLL (PLL) 和音频 PLL (PLLI2S) 输入时钟的分频系数,由软件置 1 和清零,用于在 VCO 之前对 PLL 和 PLLI2S 输入时钟进行分频。

位 14:6 PLLN:

适用于 VCO 的主 PLL (PLL) 倍频系数 (Main PLL (PLL) multiplication factor for VCO) 由软件置 1 和清零,用于控制 VCO 的倍频系数。压控振荡器 VCO(Voltage-Controlled Oscillator) 是 PLL 核心组成部分,负责根据输入电压生成高频振荡信号,其输出频率随控制电压线性变化。

位 17:16 PLLP:

适用于主系统时钟的主 PLL (PLL) 分频系数 (Main PLL (PLL) division factor for main system clock) 由软件置 1 和清零,用于控制常规 PLL 输出时钟的频率。软件必须正确设置这些位,使其在此域中不超过系统时钟最大频率限制。

位 27:24 PLLQ:

主 PLL (PLL) 分频系数,适用于 USB OTG FS、SDIO 和随机数发生器时钟 (Main PLL (PLL) division factor for USB OTG FS, SDIO and random number generator clocks) 由软件置 1 或清零,用于控制 USB OTG FS 时钟、随机数发生器时钟和 SDIO 时钟的频率。在默认的情况下,PLLQ这条线是灰色不可用的,除非你使能了USB或RNG或SDIO,此处才是可编辑状态。

时钟物理源

在MX的PCC时钟源配置界面,都是针对外部时钟源的,在使能 HSE 或 LSE 前,整个Clock Configuration 选项卡大多是灰色,时钟树上只有内部时钟的部分树枝是可以配置的。

内部时钟和驱动

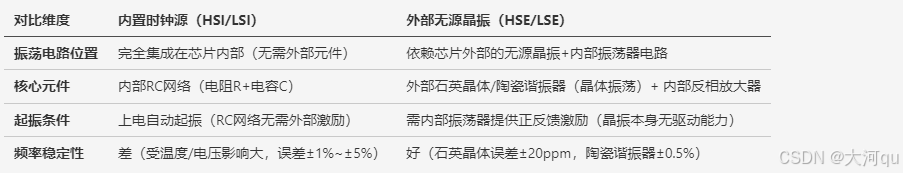

STM32是内置高低两个时钟源的,它们的震荡电路应该不是晶体震荡电路吧?

STM32内置的高/低时钟源(HSI、LSI) 的振荡电路是RC振荡器,而非外置晶振使用的晶体振荡电路。两者的核心区别在于是否依赖外部石英晶体,内置时钟源通过芯片内部的RC网络实现振荡,而外置时钟源(HSE、LSE)则依赖外部石英晶体/陶瓷谐振器(晶体振荡电路)。这种设计的主要好处在于,无需外部元件,完全集成在芯片内部,上电即可工作(无需等待外部晶振起振)。但是它们频率精度低,而且受温度和电压影响大。详细的,这里不再过多的讨论。

STM32的内置时钟源和外置无源晶振时钟源,这两种模式,它们有交集,但更多的是独立。

相同之处在于,它们会共用芯片内部的电源域和基础模拟电路(如稳压器、噪声滤波电路)。不同之处在于,核心驱动电路(振荡器)是独立的。前者的驱动电路是,高精度RC网络、低功耗反相放大器(为RC网络提供正反馈,维持振荡),驱动电路与RC网络完全集成,上电后自动起振。后者的驱动电路是,高增益反相放大器(为外部晶体提供正反馈激励,使其产生机械振动并输出电信号)、负载电容匹配电路,驱动电路本身不产生振荡(依赖外部晶体),仅通过反相放大器的正反馈使外部晶体谐振。

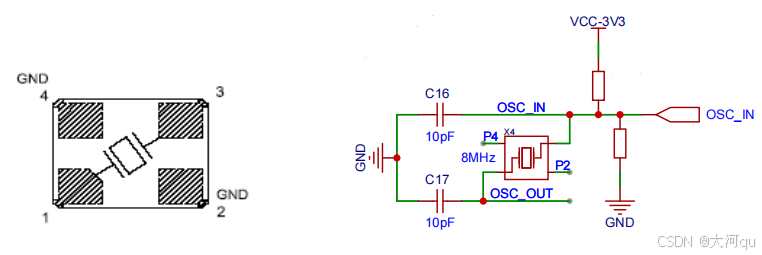

无源晶振和驱动

先来看两款无源晶振的数据手册,直观的感受下,无源晶振本质就是快石头。

32.768kHz无源晶振,8MHz无源晶振,如上链接可以下载手册。我们以TAXM8M4RDBCCT2T 为例,看看其管脚和电路原理图,

别看这小子有4个引脚,但实际上,只有两个是有效的,这是为了和有源的晶振管脚兼容,方便以后扩展,即上图P2和P4悬空或接地。无源晶振的两端接在主芯片的OSC_IN和OSC_OUT管脚之间,OSC_OUT是主芯片内部驱动电路的输出脚,以此敲打晶振动起来。

外部无源晶振的驱动电路,

是 STM32 内部集成的“晶体驱动电路”,核心是 反相放大器 和 正反馈网络。上电后,反相放大器输出噪声信号,通过正反馈网络(电容/电阻)选频,使外部晶体在其固有频率(如8MHz HSE)上产生机械谐振。晶体谐振产生的正弦波信号再次通过反相放大器放大,输出稳定的时钟信号。反相放大器的核心作用,在于提供能量和正反馈。外部无源晶体本身无能量来源,反相放大器通过 电源供电(AVDD)为晶体提供振荡所需的能量(类似“推秋千”,放大器的能量输入维持晶体持续振动)。反相放大器的输出信号通过反馈网络(如电容分压)送回输入端,形成 正反馈环路,使晶体仅在固有频率上谐振(抑制其他频率的噪声)。

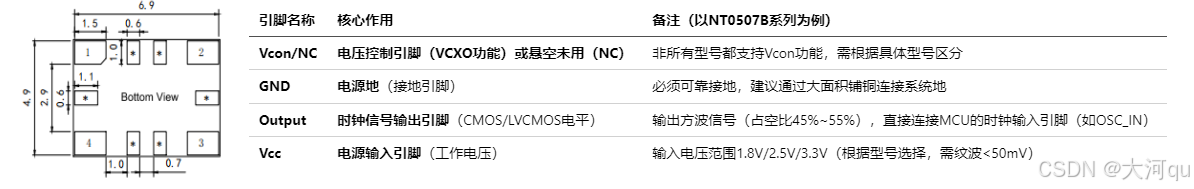

有源晶振和驱动

先来做个基本理解:这里的“源”它不仅仅是电源,应该是指 “能量和驱动来源”。无源晶振,无内置能量来源,需外部电路驱动(“借别人的力振动”)。有源晶振,自带能量转换电路,独立驱动振动(“自己有力气振动”)。因此,无源晶振需要接STM32的两个引脚(OSC_IN/OSC_OUT形成振荡回路),而有源晶振只需接一个输入引脚(自带驱动,直接送信号)。以 型号NT0507BH3I507EA10 为例,

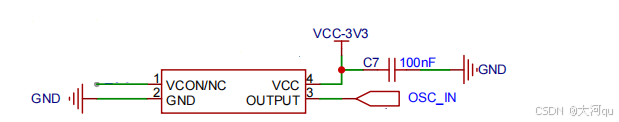

有源晶振的电路原来图,通常如下图这个样子,

管脚1,悬空或者接压控电压。在支持压控评率的情况下,为了电路板对晶振选择的兼容性,压控的引脚可能会选择 OSC_OUT管脚。

MCO 时钟信号

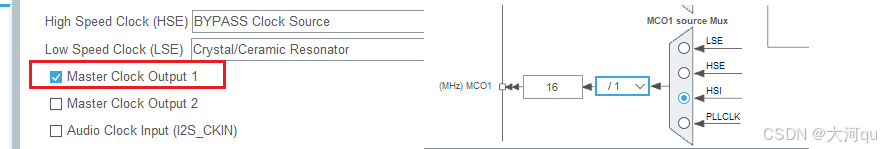

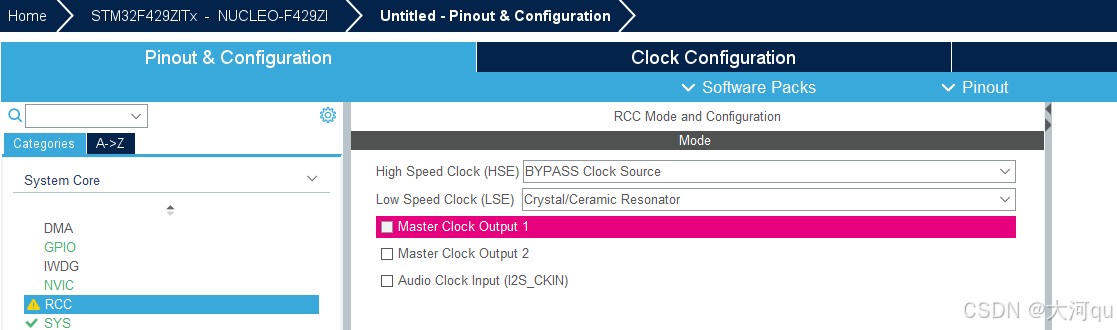

在文中前面的小节中我们讲到过一次了,MCO 是 Microcontroller Clock Output 的缩写,即,微控制器时钟输出,是STM32芯片的一种特殊功能引脚,用于将内部时钟信号(如PLL输出、HSI、HSE等)通过GPIO引脚输出到外部,供调试或外部设备使用。要使能这种时钟输出功能,首先要在RCC配置界面,启用 Master Clock Output,否则对应的时钟树是不可编辑的。

在合理的配套的硬件设计基础上,结合上述配置,就可以将自己的内外部高低时钟信号的一路,分频后,借给其他MCU使用。前文也提到过,STM32F429 的评估板就是这么干的,将ST-LINK-STM32F103的HSE,给了F429主芯片使用。此时F103/ST-LINK固件程序的时钟配置,当如上图,启用时钟输出,并进行分频配置。而F429的程序时钟配置中,与使用有源晶振时配置是相同的。

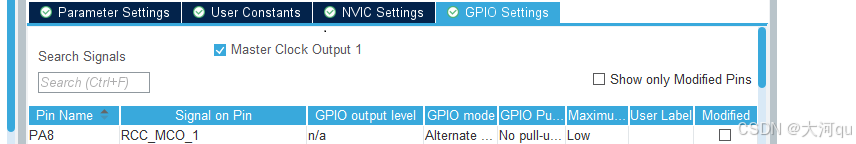

当我们在MX配置实验操作中启用 Master Clock Output 1 时,MX GPIO 配置会自动配置 PA8为MCO_1,如下图,

ST评估板也是这么搞的,

音频时钟配置

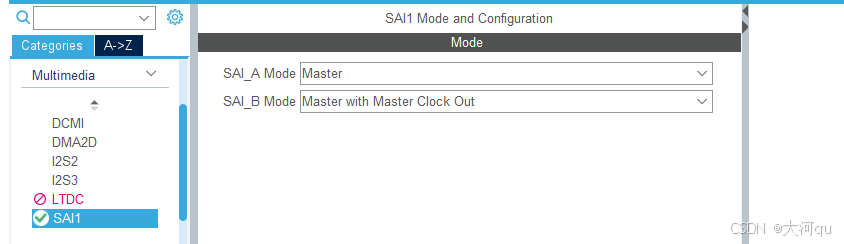

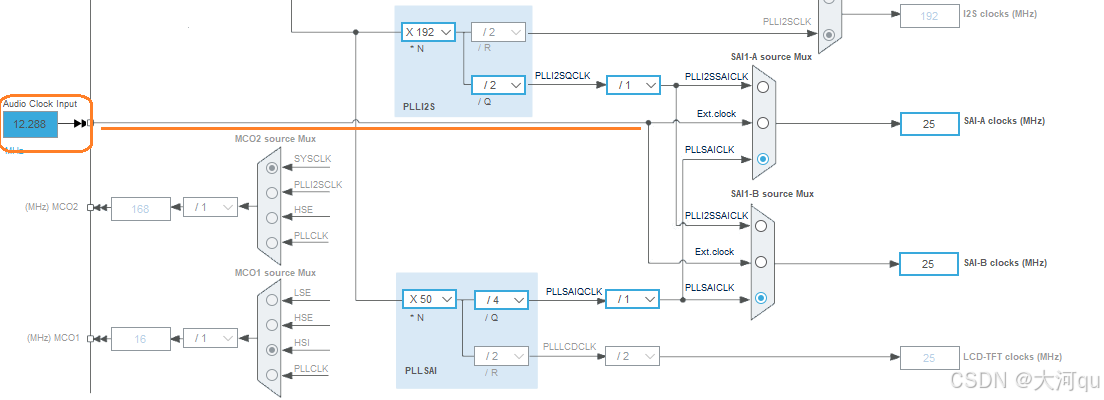

在STM32微控制器中,SAI(Serial Audio Interface,串行音频接口) 是一种高性能、多通道的音频专用接口,专为数字音频信号的传输设计,支持I²S、PCM、TDM等多种音频协议,广泛用于音频播放、录音、语音处理等场景(如智能音箱、车载音响、工业音频采集)。要启用此SAI接口后,其在时钟树中的时钟才会处于可配置状态,

SAI接口的时钟,可以从 HSE 获得,当然也可以使用独立的定时器,此时需要勾选RCC配置中的 Audio Clock Input (IIS_CKIN)选项。

音频独立时钟,不是所有型号芯片都有的,比如,STM32F103就没有,哈哈其时钟树看起来干净了许多,

晶体振荡器?

正式开谈前,必须要有的知识是,振荡电路的类型,可不止RC电路哦,常见的震荡电路类型有:

RC振荡电路:由 电阻(R)和电容(C) 作为选频网络,输出低频信号(kHz级,如1kHz~1MHz)。

LC振荡电路:由 电感(L)和电容(C) 作为选频网络,输出高频信号(MHz级,如射频通信)。

晶体振荡电路:由 石英晶体 作为选频网络,输出高精度信号(MHz级,如MCU的HSE/LSE时钟)。

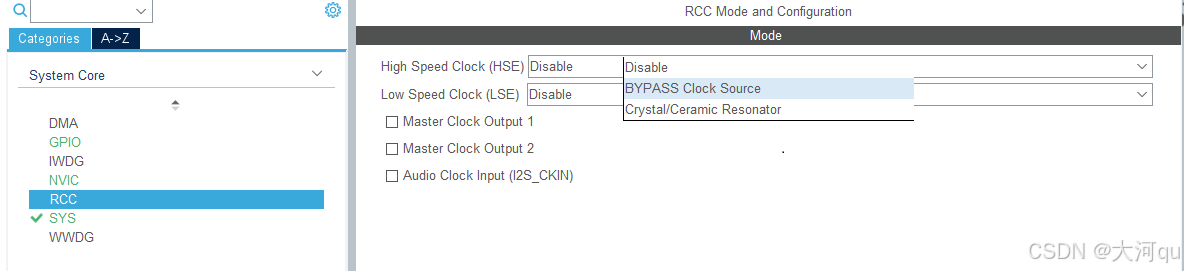

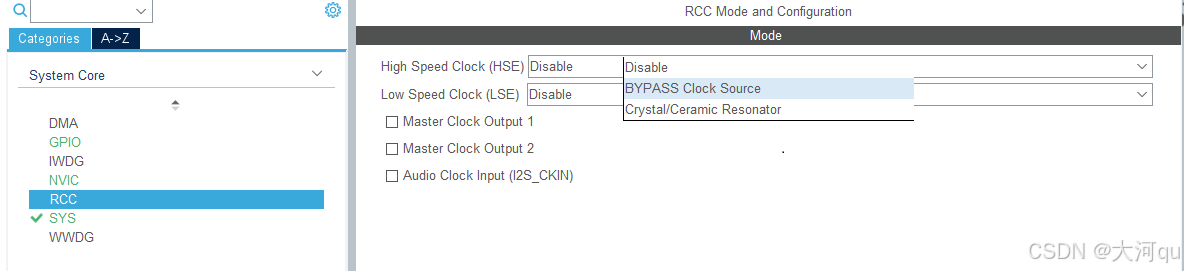

针对物理外部时钟源分类,其还会被分为晶振模式和旁路模式,此分类法的根本在于,是否使用了STM32内部晶体震荡电路。下文将围绕 Crystal/Ceramic Resonator、BYPASS Clock Source、有源晶振、无源晶振、旁路模式、晶振模式等概念及其关联展开。

外部时钟源类型

针对非专用外部时钟源(或者是可以叫外部系统时钟源吧),HSE 和 LSE 的配置选项都是下图中,Disable、BYPASS Clock Source、Crystal/Ceramic Resonator 三个选项。MX中RCC如下配置中,为什么又是依据什么,如此划分?

温习几个单词,crystal /ˈkrɪstl/ 晶体的 ceramic /səˈræmɪk/ 陶瓷的 resonator /'rɛzə’netɚ/ 共振器 BYPASS 旁路的

知识继续补充,Crystal Resonator(晶体谐振器) 和 Ceramic Resonator(陶瓷谐振器) 是两种常见的无源谐振器类型,均用于为芯片提供稳定时钟信号,通常情况下,晶体谐振器精度高、可靠性较好,但成本较高。

针对外部时钟源(HSE/LSE),将时钟源分为 “晶振模式”(Crystal Mode) 和 “旁路模式”(Bypass Mode) 的分类依据是 “外部时钟源是否需要STM32内部振荡器提供激励”,核心区别在于 外部器件是否自带振荡电路。内部时钟源的振荡电路和RC网络 完全集成在STM32内部,无需外部元件,因此不存在“是否需要内部激励”的问题。而外部时钟源需根据 外部器件的类型决定是否启用STM32内部振荡器。

RCC 如何选择

本小节算是结论先行吧。“晶振模式”和“旁路模式” 可统称为“外部时钟模式”,两者的共同目标是为STM32提供 “外部时钟源”(区别于内部时钟源HSI/LSI),因此可统称为 “外部时钟配置模式”。有源晶振或外部时钟信号,它们都是直接接收外部信号,无需借助STM32内部电路驱动,统称为旁路模式,即 MX选项 BYPASS Clock Source。由于概念泛化或者什么历史因素,无论是陶瓷谐振器还是晶体谐振器,这种无源的谐振器,都可以统称为无源晶振,无源晶振本身不产生时钟信号,需配合STM32内部的晶体振荡器电路OSC来工作,此为晶振模式,即MX选项 Crystal/Ceramic Resonator。

旁路模式-有源晶振

曾经,我有一个疑问,使用有源晶振时,应该配置为那种模式,是旁路模式吗?直接接入外部有源时钟信号(由外部电路生成,如信号发生器、另一块MCU的时钟输出),此时STM32内部振荡器电路被旁路/BYPASS,时钟信号直接从引脚输入。

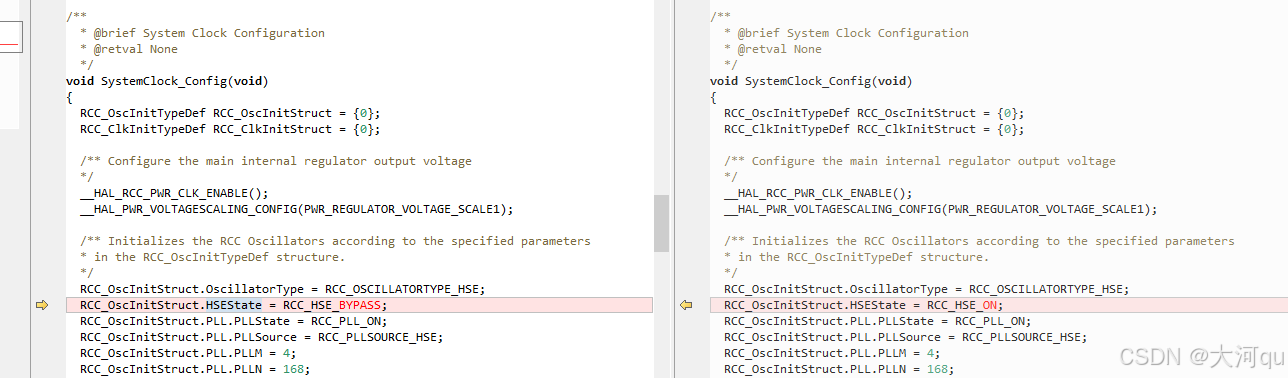

在一个工程下,我们分别将RCC配置为旁路模式和晶振模式,生成两套代码,来比较下驱动代码,看看到底哪里不同,

哈哈,全工程比较,就只有上述1行代码不同(和我的想象不太一样),我们继续追 HAL_RCC_OscConfig 函数,

*/

__weak HAL_StatusTypeDef HAL_RCC_OscConfig(const RCC_OscInitTypeDef *RCC_OscInitStruct) {.../* Set the new HSE configuration ---------------------------------------*/__HAL_RCC_HSE_CONFIG(RCC_OscInitStruct->HSEState);

}

//上述宏函数定义如下

#define __HAL_RCC_HSE_CONFIG(__STATE__) \do { \if ((__STATE__) == RCC_HSE_ON) \{ \SET_BIT(RCC->CR, RCC_CR_HSEON); \} \else if ((__STATE__) == RCC_HSE_BYPASS) \{ \SET_BIT(RCC->CR, RCC_CR_HSEBYP); \SET_BIT(RCC->CR, RCC_CR_HSEON); \} \else \{ \CLEAR_BIT(RCC->CR, RCC_CR_HSEON); \CLEAR_BIT(RCC->CR, RCC_CR_HSEBYP); \} \} while(0U)

从上述代码分析可知,RCC_HSE_BYPASS 类型是包含了 RCC_HSE_ON 类型的操作的,其包含两步寄存器位设置操作。可以粗略的认为,设置完寄存器,剩下的过程,就交给CPU就跑就行了。从外层代码看,无论是晶振/旁路模式,都要等待启振,只耗时不同吧。

旁路模式-时钟信号

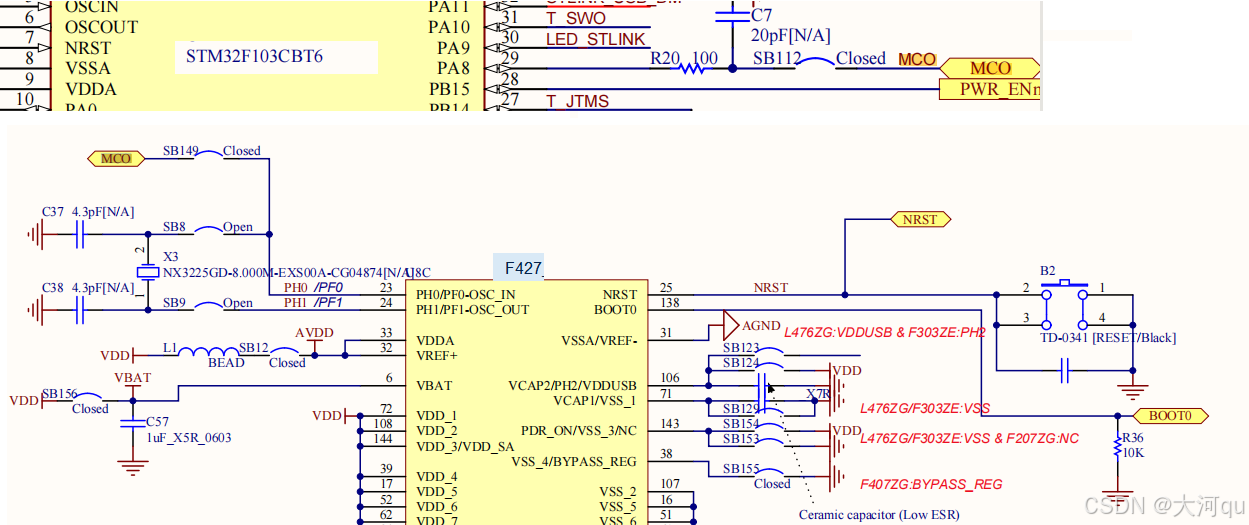

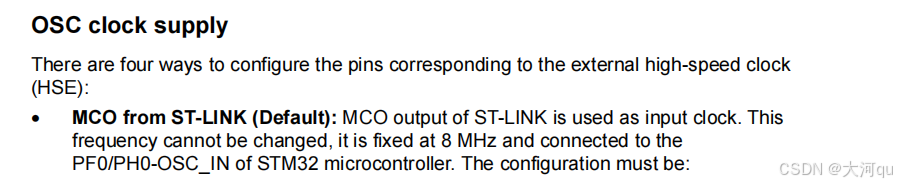

ST官方STM32F429开发板例程中,其HSE配置就是旁路模式,

通过评估板使用手册和电路原理图,可以清晰的卡到此时的旁路接线模式,

MCO 是 Microcontroller Clock Output 的缩写,即,微控制器时钟输出,是STM32芯片的一种特殊功能引脚,用于将内部时钟信号(如PLL输出、HSI、HSE等)通过GPIO引脚输出到外部,供调试或外部设备使用。评估板的STLink部分使用的是STM32F103,通过其PA8管脚完成 MCO 功能,并链接到 F429 的 PH0/PF0-OSC_IN 管脚,这就完成了时钟源旁路模式的硬件接线。另外,如果我们的板卡要共用背板上的时钟总线,此时的时钟源配置,也要是旁路模式。

频率冲突和计算

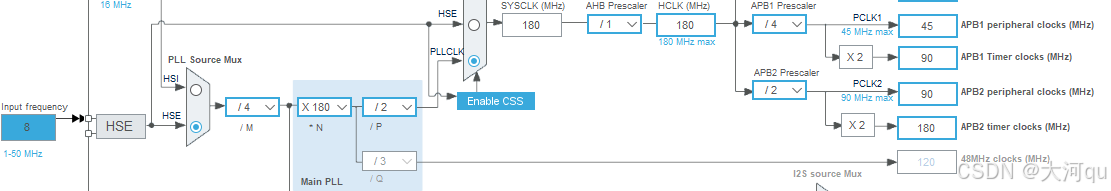

在MX时钟配置卡中,频率是会自动去计算的。但需要意识到的一点是,原始的时钟源,经过复用器、分频器、锁相环,以及MNPQ等参数的混合作用下,对于末端的频率值,可能不会满足各方需求,这时候自动频率计算就会产生频率冲突。我们以USB独立时钟和系统主时钟之间的冲突来进行说明。在启用USB2.0并配置其工作时钟的过程中,注意到一个现象,

前文提到,USB使用频率必须是48,不能是别的。这个48MHz的值,需要PLLM、PLLN,而PLLP到主时钟的线路也要用到它们,这样就可能会产生冲突。

在不启用USB的情况下,我们很容易将系统时钟配置为180MHz,

接下来我们启用USB,并配置其指定的工作频率48MHz,此时会触发以下自动时钟配置,

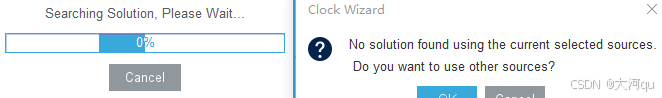

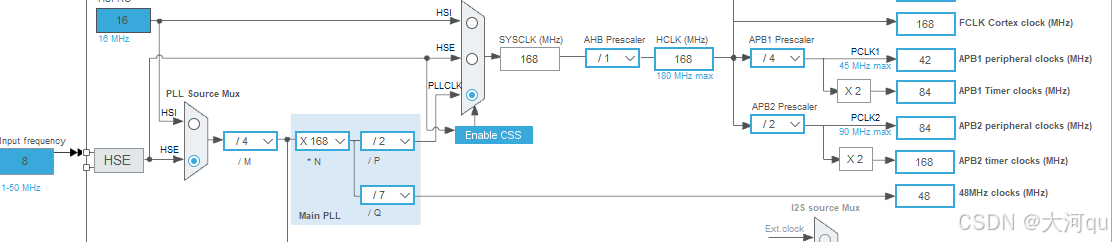

系统时钟被自动配置成了72MHz,这显然有点小啊。改回180MHz试试?

如上动图中,输入主时钟180,然后回车,MX将自动计算时钟配置解决方案,其内部可能要经过权重和多方面的分析,以得到最优解。当然也有可能无解,如上图的情况。想要PLLQ是48,同时HCLK=180,是没办法实现的。最终,

这个时候,你要去靠你的大脑做分析,并手动调整。如调整PLLN=168,然后修改USB-CLOCK和HCLK为目标值,并回车,触发自动分配。

时钟给谁用?

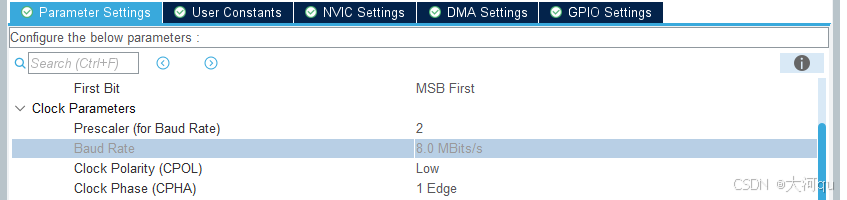

我在SPI编程实践的过程中,配置SPI时钟参数时,结合之前的知识,我给自己提出来这个问题。

这个问题看似不难回答,CPU、DMA、各种高速和低速外设都要依赖时钟来工作。更深的问题是,它们如何使用时钟?我会在后续文章中整理对于 STM32 总线矩阵架构的笔记,届时再战吧!

)

)