一、引入

(1)编码器接口的好处:

- 节约软件资源:外部中断计次,程序频繁进入中断,则软件资源会被简单频繁的工作给占用,效率不高

- 使用定时器的编码器接口,再配合编码器,就可以测量旋转速度和旋转方向

(2)编码器测速:

- 一般应用在电机控制的项目上,使用编码器测量电机的速度,然后再用PID算法进行闭环控制

- 一般电机转速比较高,会选择无接触式的霍尔传感器或者光栅

二、编码器接口(Encoder Interface)

| 作用 | 可以接收增量(正交)编码器的信号,根据编码器旋转产生的正交信号脉冲,自动控制CNT自增或自减,从而指示编码器的位置、旋转方向和旋转速度 |

| 解释 | 正交:输出两个方波信号,相位相差90度 超前90°——正转 滞后90°——反转 |

| 原理 | 测频法测正交脉冲的频率,CNT计次,然后每隔一段时间取一次计次 |

| 优点 | 可以根据旋转方向,不仅能自增计次,还能自减计次,是一个带方向的计次 |

| 特点 | 每个高级定时器和通用定时器都拥有一个编码器接口 如果一个定时器配置成了编码器接口模式,基本上就干不了其他活了 C8T6芯片只有TIM1-4总共4个计时器,所以最多只能接4个编码器 也可以通过外部中断来接编码器——通过软件资源弥补硬件资源 两个输入引脚借用了输入捕获的通道1和通道2 (编码器的两个输入引脚就是定时器的CH1和CH2引脚,CH3和CH4不能接编码器) |

| 定位 | 编码器接口模式基本上相当于使用了一个带有方向选择的外部时钟 |

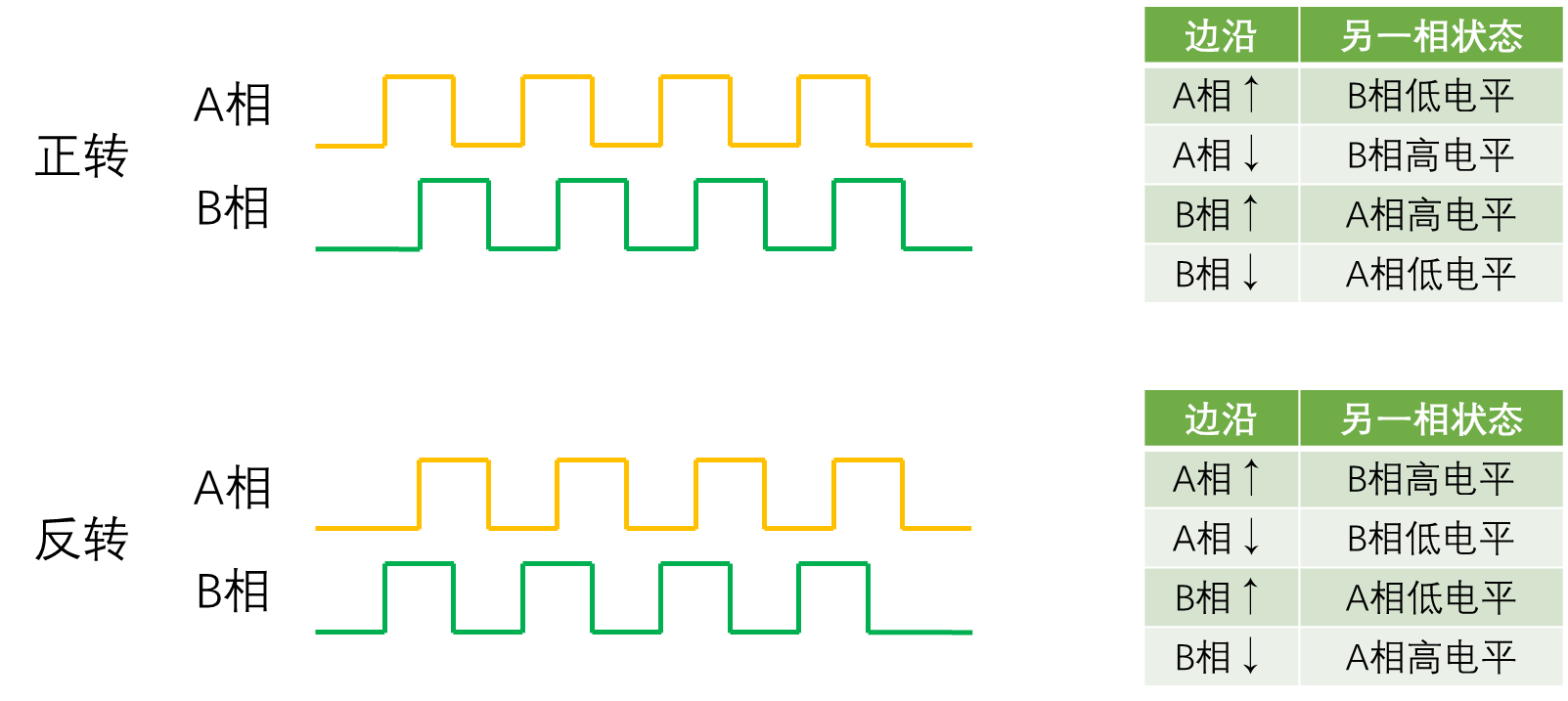

三、正交编码器

| 功能 | 测量位置、或者带有方向的速度值 |

| 配置 | 一般有两个信号输出引脚,一个是A相,一个是B相 |

| 正交信号优势 | ①精度更高:A、B相都可以计次,相当于计次频率提高一杯 ②可抗噪声:正交信号必须交替跳变,所以可以设计一个抗噪声电路,如果一个信号不变,另一个信号连续跳变,也就是产生了噪声,这时计次值是不会变化的 |

| 编码器接口设计逻辑 | ①将A相和B相素有的边沿作为计数器的计数时钟,出现边沿信号时,计数自增or自减 ②判断计数是增还是减:计数方向由另一相的状态来确定,当出现某个边沿时,判断另一相的高低电平 |

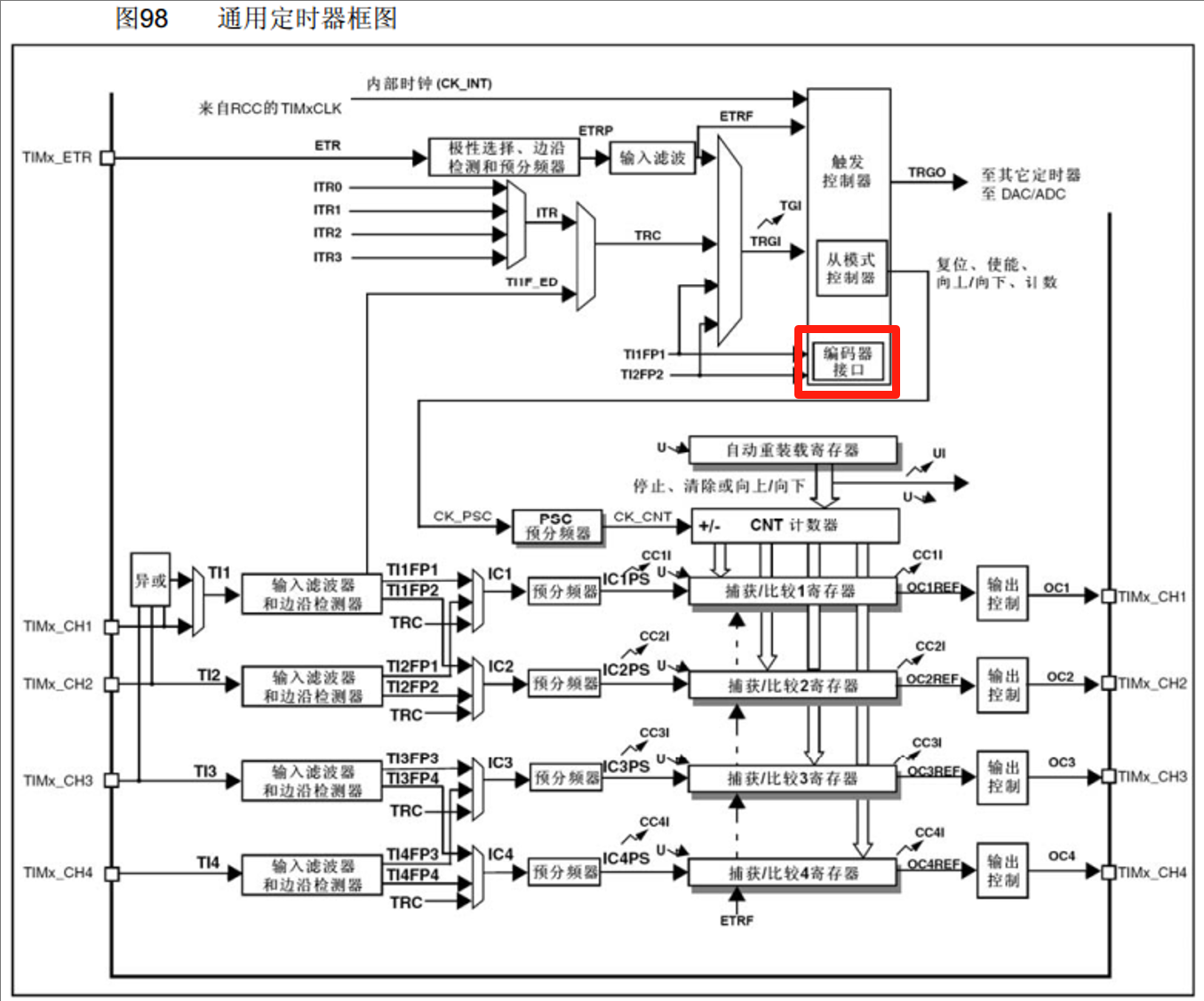

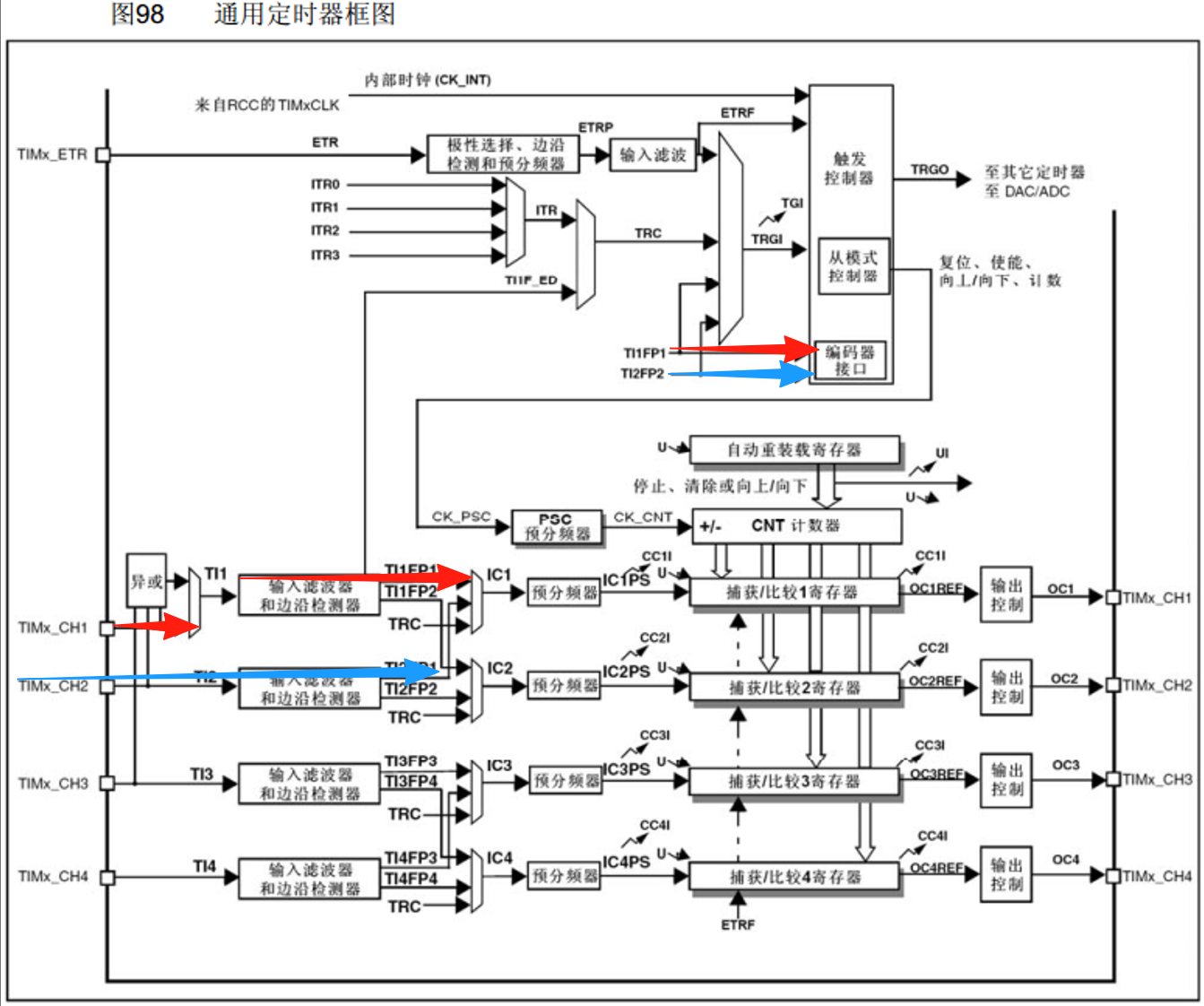

四、编码器接口的电路结构

高级定时器和通用定时器都是一样的,每个定时器都只有一个编码器接口,基本定时器是没有编码器接口

(1)编码器接口的输入连接与核心资源

编码器接口的核心功能是通过检测编码器 A 相、B 相的相位信号实现计数,其输入部分的硬件与资源关联如下:

| 编码器的 A 相、B 相分别连接到编码器接口的两个输入端,这两个输入端复用了定时器输入捕获单元的前两个通道(CH1 和 CH2),即编码器的实际输入引脚为定时器的 CH1 和 CH2 引脚; |

| 输入捕获单元的 CH3、CH4 与编码器接口无关,不参与编码器信号的处理。 |

(2)编码器接口对输入捕获资源的复用

编码器接口虽然复用了 CH1 和 CH2 通道,但并非使用输入捕获单元的全部功能,具体复用的资源包括:

| 输入捕获滤波器 | CH1 和 CH2 通道配置的输入滤波器会被编码器接口使用,用于对 A 相、B 相的输入信号进行滤波,减少噪声干扰(例如通过设置滤波系数,滤除高频毛刺)。 |

| 边沿检测电路 | CH1 和 CH2 通道的边沿检测功能(上升沿 / 下降沿检测)也会被编码器接口利用,用于捕捉 A 相、B 相信号的跳变,作为计数触发的依据 |

(3)与编码器接口无关的输入捕获资源

| 输入捕获预分频器 | 输入捕获单元的预分频器(用于控制捕获信号的分频)不影响编码器接口,因为编码器的计数触发直接由 A 相、B 相的边沿信号决定,无需对信号进行分频处理 |

捕获比较寄存器 (CCR) | CCR 是输入捕获模式下用于存储捕获时刻计数器值的寄存器,而编码器接口的核心是通过 A、B 相信号控制计数器(CNT)的增减,无需使用 CCR 寄存器 |

(4)编码器接口对计数的控制逻辑

编码器接口的输出部分本质上是一个 “从模式控制器”,其核心作用是根据 A 相、B 相的信号状态控制计数器(CNT)的计数行为(计数时钟和计数方向):

| 计数时钟 | 不依赖定时器的内部时钟(如 72MHz 内部时钟),而是以 A 相、B 相的边沿信号作为计数触发时钟 |

| 计数方向 | 不受时基单元初始化时设置的计数方向影响,而是由 A 相、B 相的相位关系决定: 当检测到某一相的边沿信号时,通过判断另一相的当前状态(高 / 低电平) 若符合 “正转” 相位关系则控制 CNT 自增,若符合 “反转” 相位关系则控制 CNT 自减。 |

此时的计数时钟和计数方向都处于编码器接口托管的状态

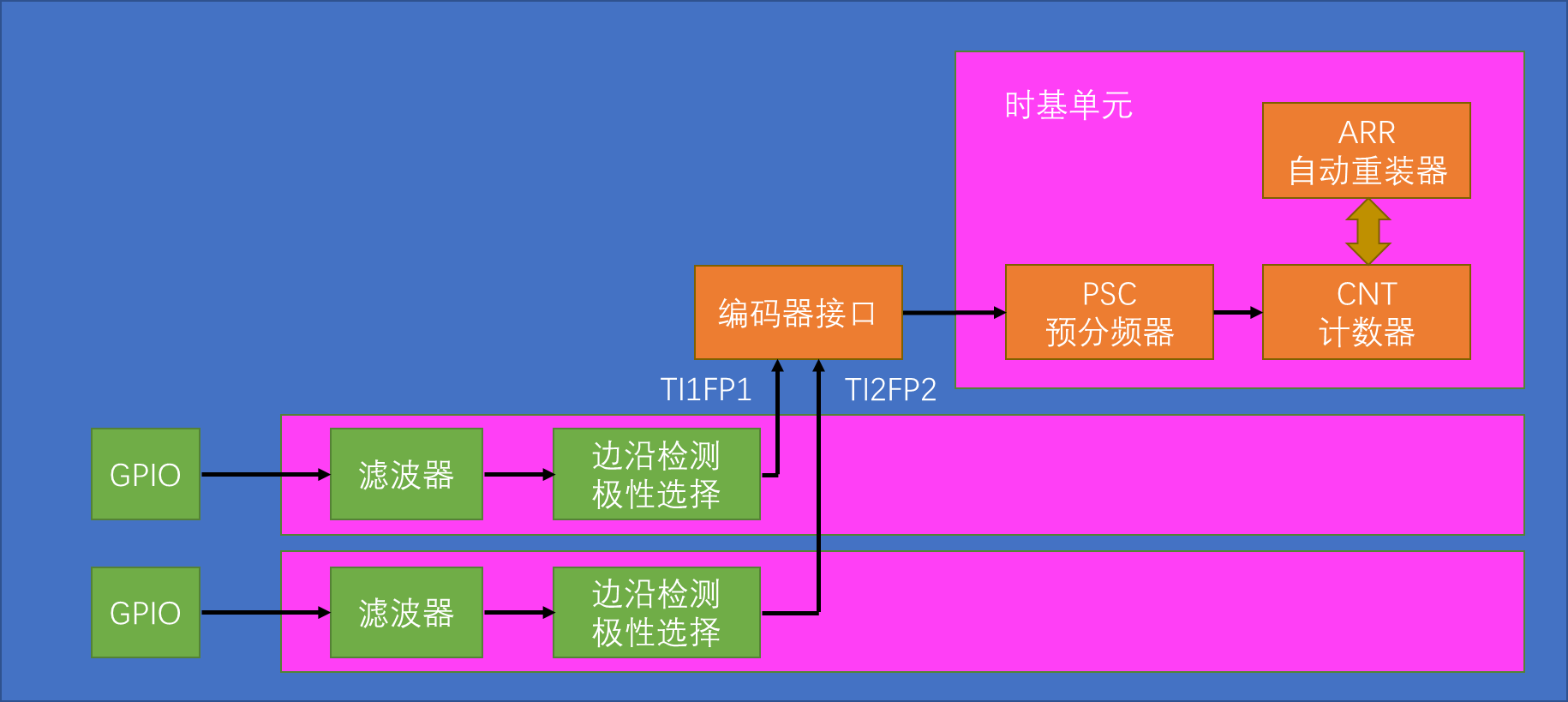

五、编码器接口的基本结构

(一)连接方式

输入捕获的前两个通道,通过GPIO口接入编码器的A、B相,然后通过滤波器和边沿检测极性选择,产生TI1FP1和TI2FP2 ,通向编码器接口,编码器接口通过预分频器控制CNT计数器的时钟,同时编码器接口根据编码器的旋转方向,控制CNT的计数方向

(二)运行逻辑

编码器正转时,CNT自增,编码器反转时,CNT自减

(三)使用补码的特性

这里ARR是有效的,一般设置ARR为最大量程65535,这样利用补码的特性很容易得到负数:

如正转,CNT正常自增;但反转CNT自减,0减一下,是65535,65534,65533

故将65535这个16位无符号数转为16位的有符号数,根据补码的定义,65535对应-1,65534对应-2,65533对应-3

六、工作细节

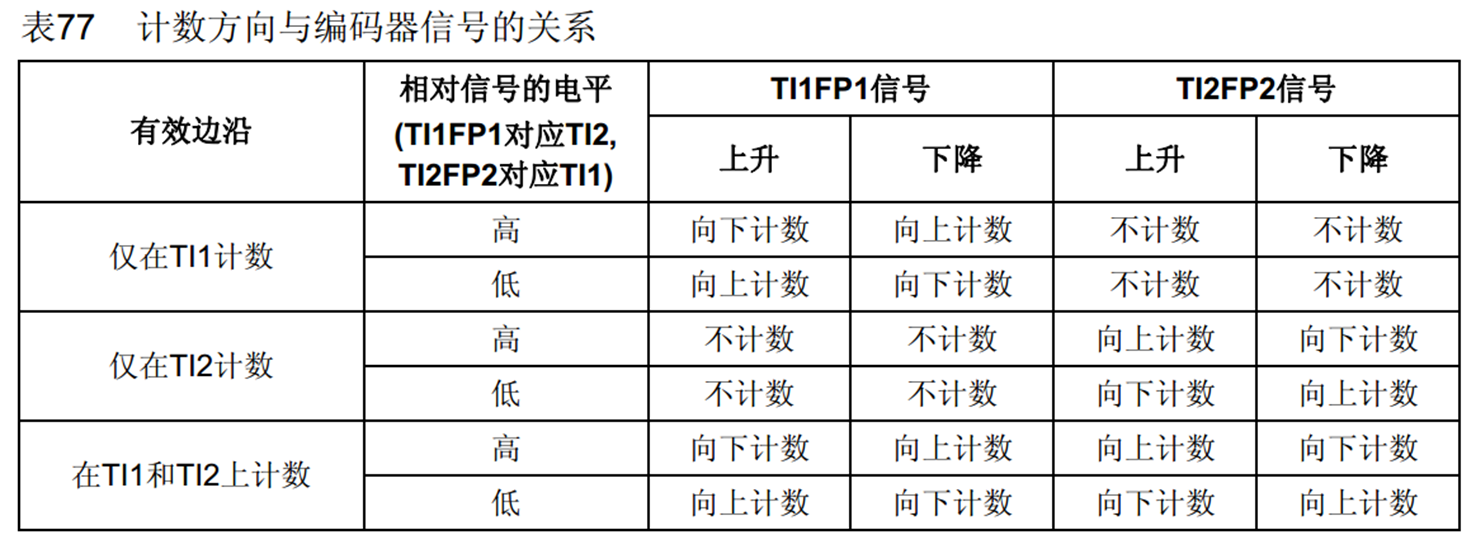

下表描述的就是编码器接口的工作逻辑

TI1FP1和TI2FP2就是A、B相,在A相和B相的上升沿或者下降沿触发计数

是向上计数还是向下计数呢?

取决于边沿信号发生的这一时刻,另一相的电平状态(即上标的相对信号的电平)

- 仅在TI1(TI2)计数,就是仅在一相的边沿技术,另一相边沿忽略,不计数

仅在TI1计数:仅在A相的上升沿和下降沿自增或自减,而B相的这两个状态忽略掉,不执行计数

仅在TI2计数:仅在B相的上升沿和下降沿计数,A相的边沿忽略,不计数

- 在TI1和TI2上计数(一般用这个模式):

如果A相上升沿、A相下降沿、B相上升沿、B相下降沿这四种状态都执行自增或自减,即A相和B相的边沿都计数,正转的状态都向上计数,反转的状态都向下计数

七、例子

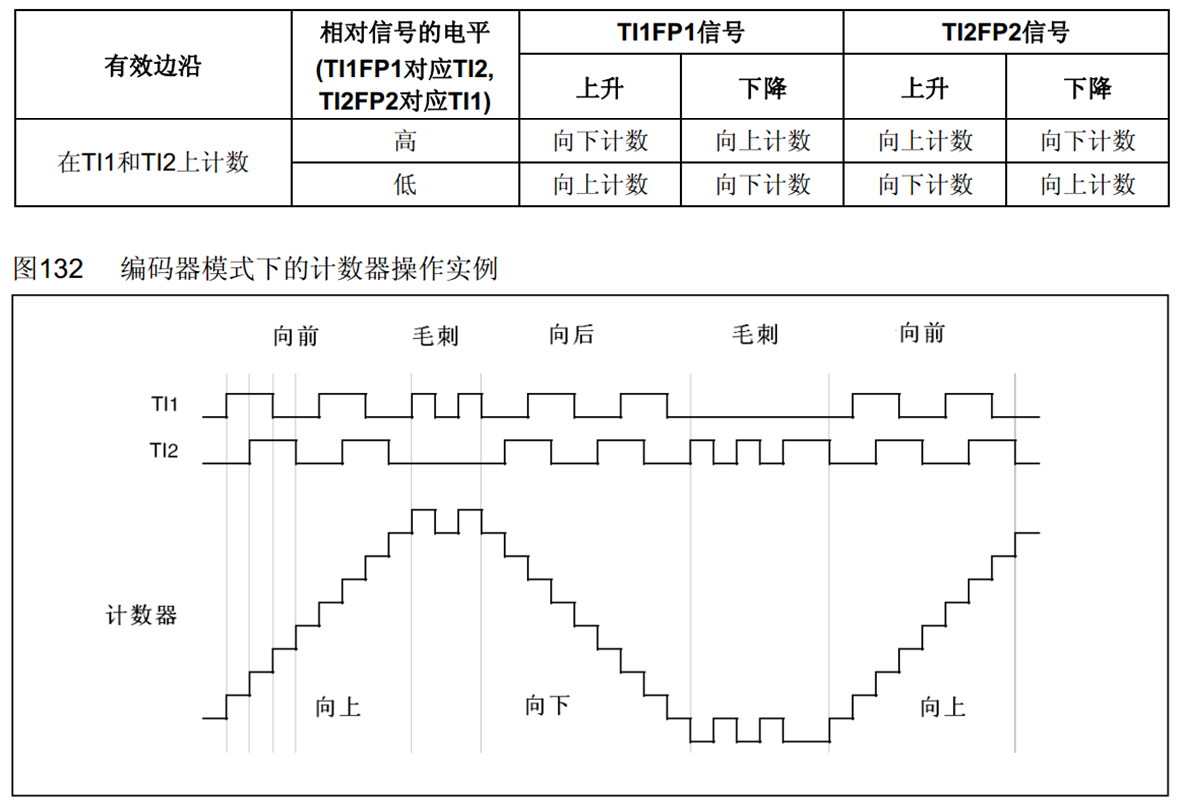

(一)实例1——两个引脚都不反相

展示计数方向逻辑与正交编码器抗噪声的原理

上图使用的就是两个引脚的边沿都计数的模式

这里是TI1和TI2的时序信号,下面是计数器值的变化情况

| 第一个状态 | TI1上升沿,TI2低电平 | 向上计数 |

| 第一个状态 | TI1高电平,TI2上升沿 | 向上计数 |

| 第一个状态 | TI1下降沿,TI2高电平 | 向上计数 |

| 第一个状态 | TI1低电平,TI2下降沿 | 向上计数 |

| 毛刺状态 | 展示抗噪声原理: TI2没有变化,TI1却跳变了好几次 这不符合正交信号的变化规律 这样就可以将这个噪声滤掉 | TI1上升沿,TI2低电平,向上计数 TI1下降沿,TI2低电平,向下计数 TI1上升沿,TI2低电平,自增 TI1下降沿,TI2低电平,自减 因此在出现毛刺现象的时候,计数器就会加、减、加、减来回摆动,最终的计数值还是原来的那个值 |

| 第三个状态 | TI2上升沿,TI1低电平 | 向下计数 |

| 第三个状态 | TI2高电平,TI1上升沿 | 向下计数 |

| 第三个状态 | TI2下降沿,TI1高电平 | 向下计数 |

| 第三个状态 | TI2低电平,TI1下降沿 | 向下计数 |

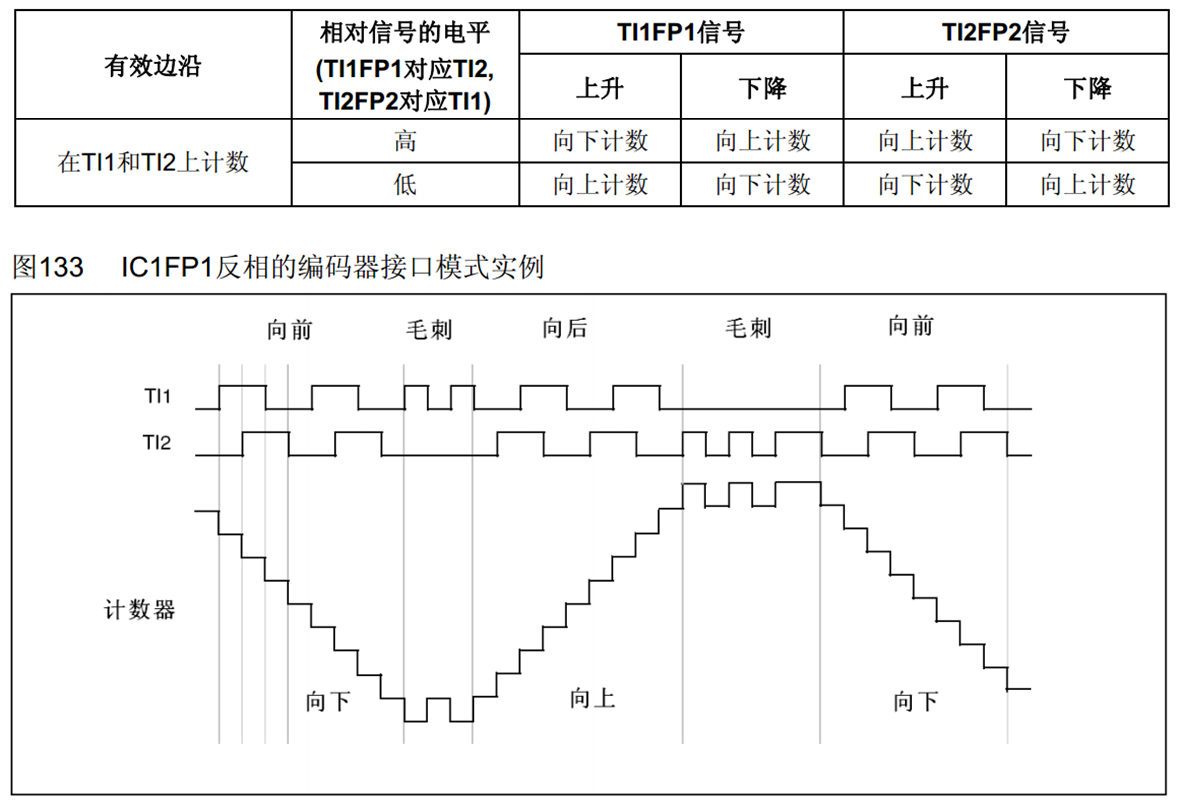

(二)实例2——TI1反相、TI2不反相

展示极性的变化对计数的影响

TI1反相是什么意思?——首先要理解这个极性选择的作用是什么

- TI1和TI2进来都会经过这个极性选择的部分,在输入捕获的情况下,这个极性选择是选择上升沿有效还是下降沿有效

- 但是编码器接口显然始终都是上升沿和下降沿都有效的,上升沿和下降沿都需要计次的

所以在编码器接口这里就不再是边沿的极性选择了,而是高低电平的极性选择

| 选择上升沿的参数 | 信号直通过来,高低电平极性不反转; |

| 选择下降沿的参数 | 信号通过一个非门过来,高低电平极性反转 |

这意味着存在两个控制极性的参数,用于决定是否对 TI1 或 TI2 的信号进行极性反转

| 均不反相 | TI1 和 TI2 都不进行反转 |

| TI1 反相 | 选择对 TI1 的信号进行处理时,即 TI1 高低电平取反,这才是反相后实际给编码器接口的电平 |

- 需要注意的是,在分析过程中,如果直接将 TI1 和 TI2 画成输入信号并对照相关表格,得到的计数方向可能是错误的。

- 因为 TI1 反相后,实际给到编码器接口的电平是 TI1 高低电平取反后的结果。

- 例如:第一个状态原本是 TI1 上升沿、TI2 低电平,经过 TI1 反相后,实际状态变为 TI1 下降沿、TI2 低电平,此时编码器会向下计数。

实例1和实例2的计数方向是相反的,这有什么用呢?

比如,当连接一个编码器时,若发现其数据的加减方向与预期相反 —— 即正转时计数器自减,反转时计数器自增,这时就可以通过调整极性来解决,只需将任意一个引脚(TI1 或 TI2)进行反相,就能实现计数方向的反转。不过,实际上想要反转计数方向,也可以直接将 A、B 相两个引脚互换。

)

Python + 地球信息科学与技术 = 经典案例分析)