软件仿真拥有最佳的信号可见性和调试灵活性,被大多数工程师熟练使用,能够高效捕获很多显而易见的常见错误。

然而,由软件实现的数字仿真过程运行速度有限,很难做到100%代码覆盖。导致那些深度隐藏的设计问题,将不可避免的逃逸,只能以FPGA在线调试方式解决。

01

为什么全局可观测能力如此重要

如果说调试是自动化最后的堡垒,那么数据则是调试的生命线。

在很大程度上,代码是写出来的,更是调试出来的。

走在异构计算、硬件加速最前沿的EDA硬件辅助验证行业,一直代表了FPGA调试验证的最先进水平。

不管是硬件仿真平台(Emulation)、原型验证系统(Prototyping),或是最新将两者功能合二为一的EP1或者P2E,使得FPGA硬件在线调试,像软件调试一样,所见即所得。

能够为用户提供与软件仿真类似的100%信号可见性,用于高效定位和修复设计问题。

如果说数字仿真器是为IC设计画素描,那么用FPGA构建的仿真加速器,则有3D立体克隆效果。但这些昂贵的高端平台,主要服务需要流片的超大规模IC设计。

近四十年来,始终不能惠及众多的FPGA应用开发人员。

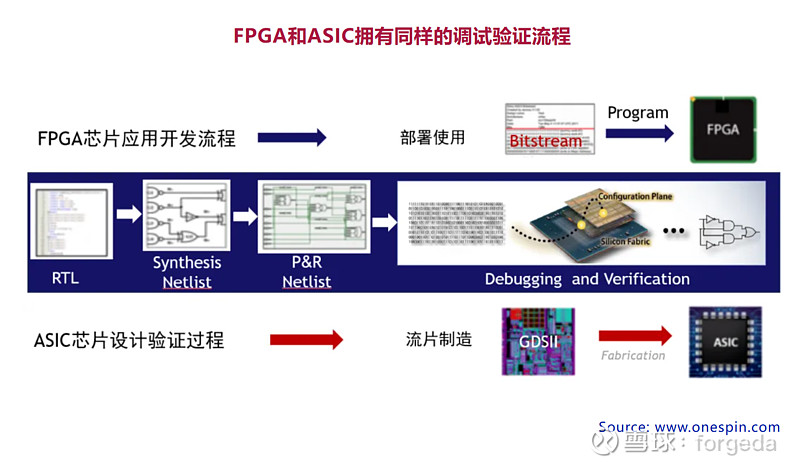

出厂状态的FPGA芯片,内部只是空白的门海阵列,用户使用时,是将设计的结果文件,即生成的位流(Bitstream)载入到芯片后,完成硬件电路的配置定制过程,与ASIC芯片的流片生产过程类似。

也被视为价格亲民的“ASIC”芯片。

不同的是,对于ASIC芯片设计,用EDA硬件辅助验证工具进行详尽的硅前验证,工程师拥有充足的武器库,尽可能实现设计的“零缺陷(Zero Bug)”,减少流片失败风险。

而FPGA用户应用开发过程中的硬件电路设计,是在自家作坊完成。

可以是团队,甚至“一人成团”的全栈工程师,完成从设计、调试、验证等全部生产“制造”流程。

全局可观测调试能力Full Visibility & Debugging,对提升设计生产力的重要作用,不言而喻。

在软件行业,如果某个系统是不可观测的,往往意味着距离“崩溃”不远了。

一旦真正出现问题,将额外花费工程师解决问题的时间成本。

但FPGA工程师除外,更像是工作常态。

与以往相比,现在的商用FPGA芯片容量规模更大,大量的功能模块、嵌入式软件、第三方IP核被集成使用,设计更为复杂。

不同于软件行业已经有大量工具和越来越多的APIs,构建整个技术栈,硬件行业还相对保守,也更为封闭。

在有限EDA工具支持下,很大程

![华为OD-2024年E卷-字符串化繁为简[200分] -- python](http://pic.xiahunao.cn/华为OD-2024年E卷-字符串化繁为简[200分] -- python)

)

比值函数atan2())

-- Java连接redis服务器)