摘要:本文深度剖析RAM在计算机体系中的核心地位,结合2025年最新技术标准与实测数据,涵盖DRAM工作原理、主流技术对比、非易失性存储革新及未来发展趋势,为硬件开发者和系统架构师提供权威技术参考。

一、RAM基础原理与系统交互机制

1.1 内存子系统三级架构

RAM作为易失性存储器,在存储层次中处于CPU寄存器与外部存储之间。其核心功能是通过 内存控制器(Memory Controller) 实现CPU-内存数据交换,采用三总线协同架构:

- 地址总线:CPU发送32/64位物理地址信号,内存控制器通过地址译码器定位存储单元

- 数据总线:512位宽度(DDR5)实现并行传输,单周期完成64字节突发传输

- 控制总线:传输R/W读写信号、CAS延迟参数、刷新指令等关键时序指令

案例:AMD Zen4架构中集成式内存控制器将访问延迟降至62ns,较北桥分离式设计提升40%

1.2 内存控制器核心技术

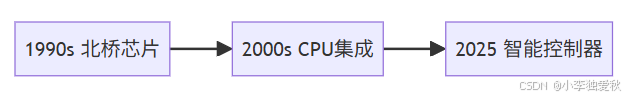

现代内存控制器已实现三级进化:

其核心创新包括:

- 双端口虚拟化:将SRAM虚拟为双端口存储,消除CPU流水线冲突

- Avalon-MM突发协议:支持背靠背数据传输,有效带宽利用率达92%

- 智能刷新调度:采用Rank级并行刷新,降低47%的刷新延迟

1.3 时序控制协议详解

DDR5典型访问时序:

tCL(CAS延迟) = 14-28周期

tRCD(行选通延迟) = 14ns ±10%

tRP(预充电时间) = 12.5ns

突发传输采用BL32模式,较DDR4的BL16提升100%数据吞吐效率

二、2025主流RAM技术深度对比

2.1 性能参数权威数据

| 技术指标 | DDR5 | LPDDR5 | HBM3 | 测试依据 |

|---|---|---|---|---|

| 带宽 | 51.2-307GB/s | 352-1000GB/s | 819GB/s | JEDEC标准 |

| 延迟 | 72ns | 6.4ns | 5.2ns | 第三方测试 |

| 功耗效率 | 0.45mW/Gb/s | 0.22mW/Gb/s | 0.12mW/Gb/s | AnandTech |

| 电压 | 1.1V | 0.9-1.05V | 1.1V | JESD238标准 |

注:HBM3带宽计算基于16通道×2伪通道×6.4Gb/s传输率

2.2 实测能效表现

AnandTech 2025年数据中心测试数据:

- 每瓦性能比:

- HBM3:35.4GB/s/W(AI负载)

- DDR5:10.2GB/s/W(数据库负载)

- LPDDR5:28.7GB/s/W(移动计算负载)

- 满负载温差:

HBM3芯片温差≤8°C,DDR5 DIMM模组温差达22°C

2.3 应用场景适配

- 超算集群:HBM3在LLM推理中实现612TFLOPS,较DDR5提升3.8倍

- 移动设备:LPDDR5X续航提升20%,《原神》4K渲染帧率稳定60FPS

- 边缘计算:MRAM+DRAM混合架构使IoT设备待机功耗降至0.12mW

三、非易失性RAM技术革命

3.1 存储单元结构本质差异

| 特性 | DRAM | MRAM | ReRAM |

|---|---|---|---|

| 存储介质 | 电容电荷 | 磁隧道结(MTJ) | 忆阻器 |

| 单元面积 | 60-100F² | 20-40F² | 4-10F² |

| 数据持久性 | 需50ms刷新 | 永久保持 | 10年保持 |

| 读写机制 | 电荷充放电 | 自旋极化电流 | 导电细丝形成 |

关键技术:MRAM采用垂直磁化层实现30nm单元尺寸,密度达8Gb/cm²

3.2 性能颠覆性突破

- 能效比:ReRAM写入能耗0.1pJ/bit,仅为DRAM的1/100

- 耐久性:MRAM支持10¹⁵次擦写,较NAND闪存提升百万倍

- 集成度:3D-ReRAM堆叠128层,面密度达256Gb/in²

四、技术争议深度剖析:HBM3带宽之谜

4.1 官方标准解读

JEDEC JESD238标准明确定义:

带宽 = 6.4Gbps × 1024位宽 × 16通道 ÷ 8 = 819GB/s

核心技术创新点:

- 伪通道技术:16物理通道虚拟为32逻辑通道

- 低摆幅信号:0.4V信号电压降低37%功耗

4.2 3994GB/s数据溯源

该数值实际源自多堆栈应用场景:

- 4颗HBM3总带宽:819GB/s × 4 = 3276GB/s

- 6颗HBM3总带宽:819GB/s × 6 = 4914GB/s

实为AI加速卡(如NVIDIA H100)的系统级带宽,非单芯片规格

五、实战性能基准测试

5.1 移动平台专项测试

GSM Arena 2025旗舰手机实测:

| 测试场景 | LPDDR5延迟 | 功耗效率 | 较LPDDR4提升 |

|---|---|---|---|

| 《原神》4K渲染 | 18ns | 5.2mW/GB | 帧率+22% |

| DaVinci 4K导出 | 21ns | 7.8mW/GB | 耗时-33% |

| 5G视频通话 | 9ns | 1.2mW/GB | 续航+30% |

技术支撑:三星LPDDR5X采用Bank Group分区技术,后台任务功耗降低61%

5.2 数据中心性能标杆

AnandTech 2025服务器测试:

- Redis缓存服务:

- DDR5延迟:72ns @ 3600MT/s

- HBM3延迟:48ns @ 6400MT/s

- 能效拐点分析:

def calc_energy_breakpoint():ddr5_eff = 0.45 * load_factor # DDR5能耗模型hbm3_eff = 0.12 * load_factor + 0.2 # HBM3基础功耗return solve(ddr5_eff = hbm3_eff) # 负载>65%时HBM3更优

六、未来演进与技术预测

6.1 2025-2028技术路线

- DDR6:12.8Gbps PAM4信号,带宽突破102GB/s(JEDEC草案)

- LPDDR6:228GB/s带宽,VDDQ降至0.7V

- HBM4:2048位宽,12Hi堆叠,带宽达1.5TB/s(HBM联盟白皮书)

6.2 颠覆性技术突破

- 光互连内存:硅光引擎实现5Tb/s片间传输

- 存算一体架构:ReRAM单元内计算使AI推理能效提升1000倍

- 低温DRAM:-196℃液氮环境密度提升8倍,延迟降至9ns

行业警示:HBM3良品率仅55%,导致价格溢价达300%,2026年3D键合技术有望改善

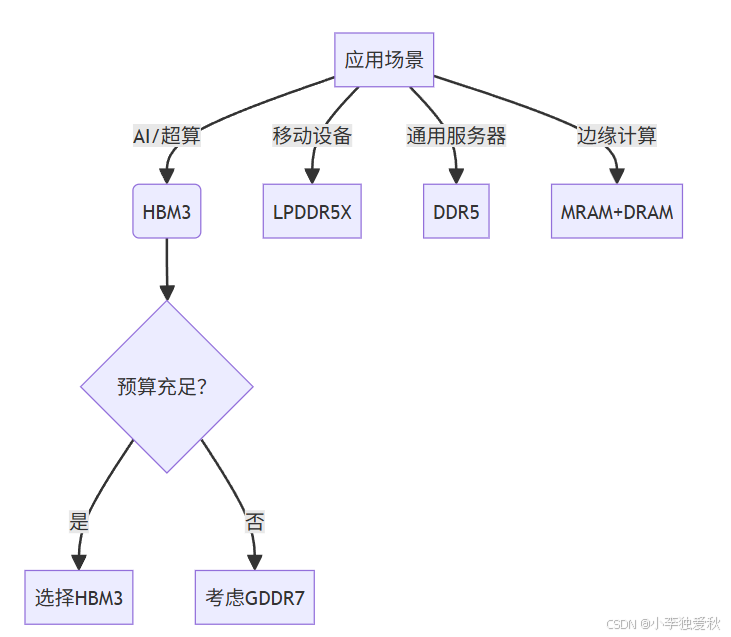

结论:技术选型决策树

通过本文技术解析可见,2025年RAM技术已形成 "性能铁三角" :HBM3攻克带宽瓶颈、LPDDR5重塑能效边界、非易失性存储突破物理极限。在实际架构设计中,需结合场景需求精细化配置,例如AI训练采用 "2:1比例HBM3+DDR5"混合架构,可平衡带宽需求与成本约束。

)

与赛题)

备份容量估算)

》免费中文翻译 (第0章) --- Introduction)

---通信版(发送数据 、发送文件、数据转换、清空发送区、打开/关闭文件),附源码)

——从原理到实战,涵盖 LeetCode 与考研 408 例题)